引言

目前,大多数LED视频系统都是通过 VGA接口从计算机获取数据源,但在LED显示系统中,信号经过多次转换,难免会造成一些图像细节的损失。

DVI(数字视接口)的工作原理就是将显卡产生的数字信号原封不动地传输给数字显示器,在信号传输过程中没有任何信号损失,并且能有效防止外界杂散信号的干扰。因此,研究设计基于DVI接口的LED视频控制系统有较强的实用价值。

DVI概述及工作原理

DVI是由 DDWG(数字显示工作组)组织制定的高速数字信号传输接口技术,有DVI-D 和DVI-I 两种不同的接口形式。目前应用主要以DVI-D为主。

DVI 采用T.M.D.S.(转换最小差分信号)技术来传输数字信号。T.M.D.S.是一种微分信号机制,可以将像素数据编码,并通过串行连接传递。DVI 接口协议支持单链路 T.M.D.S.和双链路 T.M.D.S.两种方式。单链路的传输速率可达 4.9Gbps,具有3个数据通道及1个频率信号对。单 T.M.D.S.链路只提供 24位色深,当用户要求的色深超过 24位时,并且系统已经确认显卡和显示器都支持双链路T.M.D.S.时,系统会启动双 T.M.D.S.链路。本系统仅用到单链路。

控制系统设计

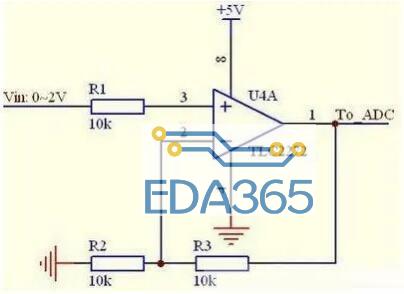

本系统由视频源、解码、数据处理与显示控制三部分组成,如图1所示。

图1 系统原理框图

解码模块

DVI 接口支持即插即用功能,要求接收设备符合VESA的DDC2B或更高版本的通讯协议,DDC2B构建在I2C总线上,通过DDC(显示数据通道)通道来传递显示设备的EDID(扩展显示标识数据),从而实现PC机对显示设备的识别和正确配置。EDID内部包含了显示设备的EDID版本信息、色度系数,以及可支持的分辨率、场频、行频等参数。

EDID数据存放在DVI解码电路的AM24LC02芯片中,该芯片为2Kb(256×8),I2C 总线、CMOS工艺的串行EEPROM存储器。电源VCC的范围为 2.7V~5.5V,可以通过把 WP引脚接电源来对整个存储器写保护,此时,存储器的内容不可更改。将DVI接口插座的第16脚(热插拔检测端)通过1KW上拉电阻和第14脚(+5V电源端)相连,构成显示设备的HPD (热插拔检测)信号。AM24LC02芯片的时钟线(SCL)、数据线(SDA)和DVI接口插座的第6、7脚相接,当系统上电时,AM24LC02 在时钟 SCL 的同步控制下通过 DDC 通道向PC机传送 EDID数据。只有当PC机识别和正确配置后,TDMS链路才会被激活。

TFP101A 是一种T.M.D.S.信号接收芯片,通过检测DE信号的状态转变来确定链路的激活状态。如果106个像素时钟过后,DE状态未发生变化,则认为链路未激活,输出SCDT (同步检测指示信号) =0;在SCDT=0的情况下,如果发现在1024个像素时钟内DE信号有两次转变,则认为链路已激活,输出SCDT=1。RX2-和 RX2+表示红色数据的差分信号,RX1-和 RX1+表示绿色数据的差分信号, RX0-和 RX0+表示蓝色数据的差分信号,分别与DVI接口的单链路通道相接(1、2、9、10、17、18脚);RXC-和 RXC+是表示时钟的差分信号,与链路时钟相接(23、24脚)。TFP101A内部锁相环回路从时钟通道获得同步时钟,为后继的T.M.D.S.码元数据恢复、像素时钟同步以及T.M.D.S.信号解码提供参考时钟,同时也作为前端锁存器对输入信号进行4倍过采样的参考时钟,T.M.D.S.解码器将 10位的串行T.M.D.S.编码解码成8位并行像素数据以及相应控制信号,并从输出接口电路将像素数据、控制信号、场同步信号和行同步信号并行输出。

数据处理与显示控制模块

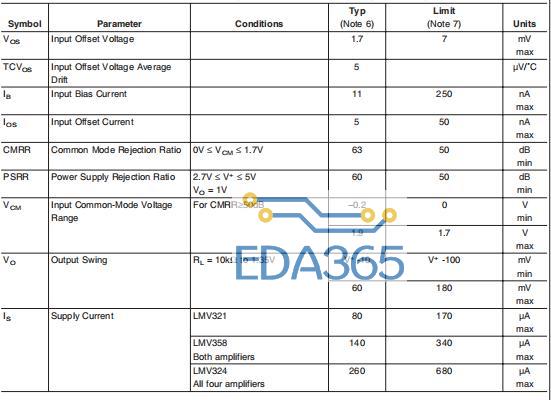

数据处理与显示控制模块主要负责对显示数据作进一步地转换、处理,产生符合 LED显示屏灰度级显示的数据,并将其送入驱动电路。数据处理与显示控制模块原理图如图2所示,主要由数据缓冲处理(双口RAM)、读/写控制、灰度扫描控制、驱动4部分组成,SRAM1、SRAM2 作为帧数据存储器。

图2 数据处理与显示控制模块原理图

虚线框内的 FPGA 控制器内部的程序流程图如图3 所示。主要完成的功能有四个。

图3 FPGA控制器程序流程图

一是数据重构。由于本设计采用占空比的方法来实现 LED显示屏的灰度,每个像素由红色(R)、绿色(G)、蓝色(B)各 8位的二进制数组成,所以计算机一帧的视频数据信息,在 LED 屏上就需要分 8 次来显示,依次为 bit0、bit1、bit2、…bit7,通过控制这些不同位视频数据信息点亮 LED 时间的不同来实现灰度。因此,需要数据缓冲处理模块(双口RAM)对每帧图像数据进行重构。

二是截取视频源。由于本设计选取的视频源分辨率为1024×768,刷新率为65Hz, LED屏大小为320×128。所以像素数据写入双口RAM的同时,需根据所要显示的LED屏大小,对重构的像素数据进行相应截取并存入帧存储器。

三是读写控制。当行同步信号HSYNC和数据使能信号DE同时有效时,读/写地址计数器同时开始计数。采用ping-pang逻辑,某一时刻帧存储器A从缓冲区接收数据时,按照分区扫描的规则读取帧存储器B内的像素数据,并经并/串转换后发送至LED屏。两者轮流切换,保证了数据的高速传输。

四是灰度扫描控制。本设计采用占空比控制方法来实现 LED 屏的灰级,整个屏可以分成 8 个区,每个区 16行,每一行每一列的数据可用 8位的二进数表示。对于每一区首先扫描显示 16 行各列 8位灰度值的 D0 位,然后扫描显示 16 行各列灰度值的 D1 位。依次类推,直到扫描显示 16 行各列灰度值的 D7 位。且8个区的扫描是同时进行的。

结语

本设计通过对 DVI 接口技术的深入研究,探讨了基于 DVI 接口的LED 视频控制系统方案。该控制系统取代了传统的VGA接入方式,运用显卡的DVI接口作为数据源,不需要进行 A/D转换和处理,减少了信号损失。因此,不论从信号质量还是后处理考虑,都有利于提高整个显示系统的性能。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多