1、 引言

USB2.0规范的推出极大地刺激了包括各类计算机外设在内的多种电子消费产品的开发设计, USB已成为微机和众多电子设备的重要标准接口。目前国外一些大公司已陆续推出了符合USB2.0规范的接口芯片,但国内对该领域的研究尚处于较初级的阶段。本文对USB IP核设计方法,提出了一种USB2.0设备接口IP核固件的实现方案,该方案采用合理定义的层次模型并已被实现,实验结果表明该方案具备良好稳定性和可扩展性的固件结构。

2 、USB2.0设备接口IP核的设计

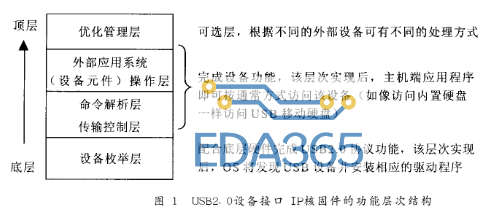

USB2.0设备接口芯片IP核分为硬件和固件两大部分。其中硬件部分主要完成USB2.0协议中的链路层功能;而固件除协助硬件完成USB2.0协议外,还负责解释设备子类协议,并实现对具体外部应用系统(设备元件)的操作。

从硬件结构分析,基于增强型8051MCU核的 USB2.0设备接口芯片(IP核)应包括以下几个模块:

(1)USB2.0传输宏单元接口模块UTMI(USB2.0 Trans ceiv er Macrocell Interface): USB2.0 IP核与USB总线之间的接口,负责接收USB2.0总线上的高速串行数据;

(2)串行接口引擎模块SIE(Serial In ter face Engine):一方面与UTM接口进行USB总线上的包级处理和传输级处理;另一方面与内部的端点缓冲及MCU进行交互;

(3)端点缓冲模块Endpoint_Buffer:存放与主机端交互的数据;

(4)通用可编程接口及多总线模块GPIO- &MultiBus:IP核与外部应用系统(设备元件)之间的联系通道,包括DMA控制模块;

(5)微处理器模块MCU及其接口模块MCU_

Bus:MCU(8051核)中固件将配合其他各硬件模块完成所需功能。

USB2.0设备接口IP核固件不仅要完成与主机的通信,还要实现对外部应用系统(设备元件)操作,因此,IP核固件可分为以下三大模块。

(1)USB传输处理模块:接收并分析底层硬件送来的各种信号(如SIE送来的各种中断请求),负责将Endpoint中接收到的主机命令/数据向上传送到主机命令解析模块,并在需要时向主机返回命令处理结果;

(2)主机命令解析模块:分析处理USB传输处理模块送来的主机命令,并负责将命令执行结果返给USB传输处理模块;

(3)设备应用处理模块:根据主机命令发送具体操作信号到外部应用系统(设备元件),并返回外部器件的状态/数据。

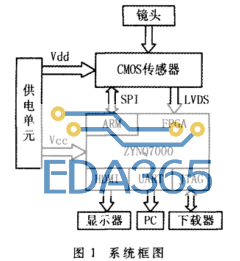

为使固件系统充分稳定并具有良好的可扩展性,我们将固件抽象为设备枚举、传输控制、命令解析、外部应用操作等几个层次,如图1所示。

3、 USB大容量存储设备固件的设计与实现

本IP核固件采用的是Windows OS支持的Bulk-Only传输协议及SCSI命令集。

3.1 固件总流程

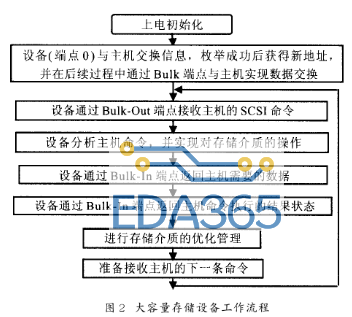

图2所示为USB大容量存储设备固件工作流程。

该固件涉及到对4个主要中断的处理,即 Com mand端点0的In 中断和Out中断、Bulk-In端点中断和Bulk-Out端点中断。其中端点0主要用于设备枚举过程中主机与设备的交互,Bulk端点则用于枚举成功后主机与设备的交互。

3.2 设备枚举层流程

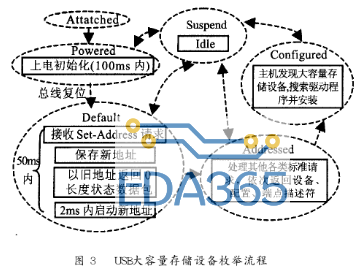

图3所示为USB设备的枚举流程。设备从接入 USB电缆开始,依次经过Attached、Powered、Default和Addressed几个状态,最终进入Configured态成为可用设备。

枚举过程中所需的各种描述符表可由用户设置后存放在指定存储单元。

3.3 Bulk-Only传输控制层流程

设备枚举成功后Bulk端点开始工作。设备端 Bulk-Only工作流程如下:

1.主机通过Bulk-Out端点发出命令包CBW;

2.设备接收CBW,解析其中包含的SCSI命令;

3.设备执行SCSI命令,如需要,通过Bulk端点完成Data交换;

4.设备根据SCSI命令执行情况通过Bulk-In端点返回命令状态包CSW给主机;

5.设备等待主机的下一个CBW。

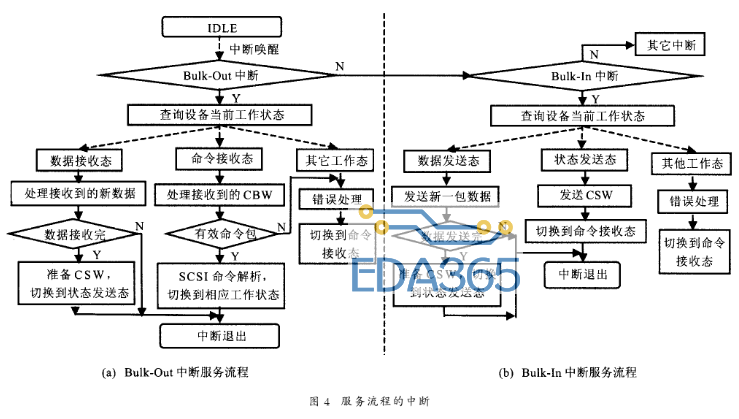

图4所示为Bulk-In和Bulk-Out中断服务流程。其中涉及到USB设备的几种工作状态有:

(1)命令接收态:本次命令处理完(已返回 CSW),设备等待下一次主机命令。在该状态下,设备将等待Bulk-Out中断,试图从Bulk-Out端点接收一个有效的CBW。

(2)状态发送态:本次命令已执行完毕,等待主机索要CSW。在该状态下,设备将等待Bulk-In中断,试图从Bulk-In端点发送一个有效的CSW 给主机。

(3)数据接收态:设备通过解析主机命令得知主机将发送数据,于是设备等待接收数据。在该状态下,设备将等待Bulk-Out中断,试图从Bulk-Out端点接收一个或一批数据。数据接收完后设备将根据具体情况确定命令执行结果状态。

(4)数据发送态:设备通过解析主机命令得知主机将索要数据,于是设备准备发送数据。在该状态下,设备将等待Bulk-In中断,试图从Bulk- In端点发送一个或一批数据。数据发送完设备将根据具体情况确定命令执行结果状态。

(5)异常状态:当发生某些不可预知的错误时,设备进入异常态,并将根据不同错误类型采取不同措施试图从错误中恢复。

3.4 SCSI命令解析(层)流程

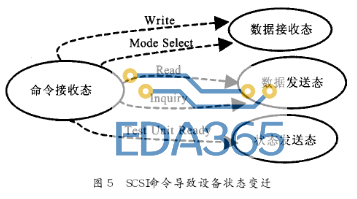

对某种特定的大容量存储设备来说,一些无意义的SCSI命令可以不必处理(实际上主机也不会使用这些命令)。设备在接收到有效的SCSI命令后,将根据命令的不同要求为数据的发送或接收做好准备,并切换到下一个有效的工作状态,如图5 所示。

3.5 对存储介质的读写操作及优化

设备固件在正确分析主机送来的SCSI命令后,可能会对存储介质进行读、写、擦除等操作。为进一步提高存储介质的读写速度,本固件方案还对存储介质操作进行了有效的优化:

(1)大批量数据读写时采用了DMA方式;

(2)对写操作需时较长的存储介质(如 FLASH)采用了中间缓冲,以减少写操作次数或将写操作移至后台进行;

(3)对存储介质上的磁盘碎片定期进行优化整理。

合理地组合应用这些方法可以有效地改进介质访问的效率。

4、结论

上述大容量存储设备的IP核固件已成功实现,其硬件基础是具有自主版权的、含MCU51核的USB设备接口IP核,固件采用Keil51C语言和51汇编语言混合完成。该固件采用分层设计,可以较容易地根据具体应用环境替换其中某些层次的代码模块,具有较强的移植性和实用性。为保证IP核固件具有一定的“健壮性”,实现过程中还需要注意仔细设计其中的错误检测和错误恢复机制,包括如何合理安排众多的中断源、如何充分考虑协议中规定的操作时间限制、如何处理Watch Dog溢出等等。

本文讨论的USB2.0设备固件方案不仅有效改进和提高了USB设备的设计开发水平,还可广泛应用于USB2.0设备接口的实际应用设计,具有良好的理论和应用价值。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多