1、引言

在以往的DSP设计中,采用TTL、CMOS电路和专用数字电路进行设计时,器件对电路的处理功能是固定的,用户不能定义或修改其逻辑功能。但随着电子技术的发展和工程对所需功能复杂程度的进一步提高,系统将需要很多芯片,这样,在芯片之间,以及芯片和印刷电路板的布线和接点也相应增多,因而导致系统的可靠性下降和功耗增加,这样也就越来越不能满足工程实际的需要。而大规模可编程逻辑器件PLD:Programmable Logic Device 和基于芯片的EDAElectronic Design Automatic电子设计自动化 工具软件则可以解决这一问题。半导体技术的提高使ASICApplication Specific Integrated Circuit:特定用途集成电路 设计技术日趋完善,同时可编程逻辑器件在结构、工艺、集成度、功能、速度、灵活性等方面的改进和提高,也为高效率、高质量、灵活设计数字系统提供了可靠性。此外,CPLDComplex Pro-grammable Logic Device 或FPGAField Programmable Array 技术的出现,又为DSP提供了一种崭新的方法,并使CPLD或FPGA设计的DSP系统具有良好的实用性和极强的实时性。

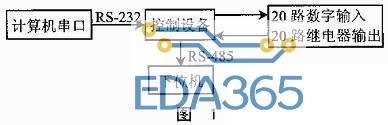

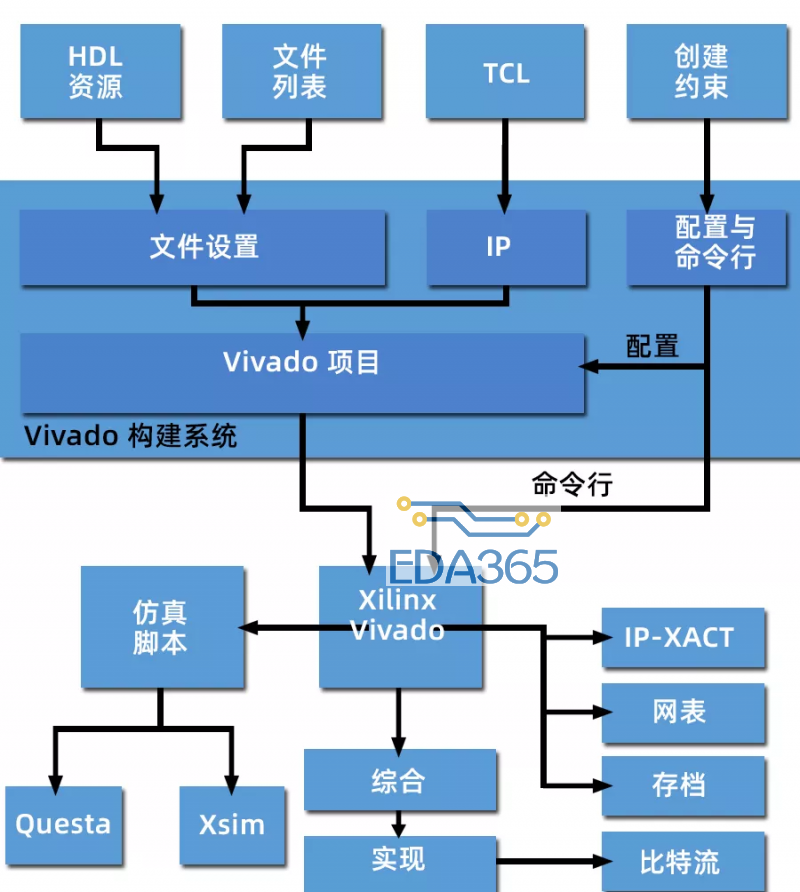

在Protel99se嵌套的PLD99的开发环境下,可编程逻辑器件设计可以直接面向用户要求,自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成能够下载到器件的JED文件,该方法结构严谨,易于操作,其设计流程如图1所示。

2、实例介绍

在某工程中,要求利用SYN0,SYN1,SYN2,SYN3,SYN4,SYN5作为同步信号进行64个通道的选择,以使64个通道在不同时刻进行工作,电路产生的发射脉冲连接在64个双晶探头上,然后将双晶探头产生的原始回波信号a1,b1,c1,d1经过AD8184四选一开关

输出到信号板进行处理。

3、设计过程

3.1 确定设计目的

由于每一通道的电路都是相同的,考虑到硬件电路以及电路板容量的问题,可先将64个通道分成16组,即每块电路PCB板设计四个通道,这16组利用SYN2,SYN3,SYN4,SYN5和拨码开关S1选通,然后利用SYN0,SYN1产生选通每块电路板的四个通道的选通信号A0、A1和输出使能EN,其电路原理如图2所示,信号的先后次序及逻辑关系见图3。

3.2 PLD器件的选择和输入输出的确定

由于CUPL语言与器件和生产厂家无关,根据设计目的和要求,最简单、最常用的GAL22V10可以作为目标器件。根据GAL22V10的技术资料和器件各个管脚的定义,可将同步信号SYN0,SYN1,SYN2 ,SYN3,SYN4,SYN5和拨码开关S1的四个管脚作为输入信号,即选择2~11为输入管脚,13脚直接接地,14~20为输出管脚,其中14~17脚用来进行通道选择,18、19脚作为AD8184的选通信号,20脚作为AD8184的输出使能,参见图2。

3.3 创建包括头信息的源文件

在PLD99的开发环境下,根据上述设想及管脚分配,利用Protel99se模板和硬件描述语言CUPL定义输入输出管脚,以创建包括头信息的文本文件Tan-Shang.pld,然后用CUPL语言写出如下的中间变量逻辑式和逻辑等式注:由于描述变量EN的乘积项过多,故将变量EN分成中间变量EN1和EN2 ,并完善文本文件。经过一系列设置后便可编译原文件,编译成功后会提示Compilation successful,方法如下:

/** Declarations and Intermediate Variables **/

EN1=!(k1 & k2 & k3 & k4 & syn2 & syn3 & sy

n4 & syn5

#!k1 & k2 & k3 & k4 & !syn2 & syn3 & syn4

& syn5

#k1 & !k2 & k3 & k4 & syn2 & !syn3 & syn4

& syn5

#!k1 & !k2 & k3 & k4 & !syn2 &!syn3 & syn4

& syn5

#k1 & k2 & !k3 & k4 & syn2 & syn3 & !syn

4 & syn5

#!k1 & k2 & !k3 & k4 & !syn2 & syn3 & !syn

4 & syn5

#k1 & !k2 & !k3 & k4 & syn2 & !syn3 & !s

yn4 & syn5

#!k1 & !k2 & !k3 & k4 & !syn2 &!syn3 & !

syn4 & syn5

EN2=!(k1 & k2 & k3 & !k4 & syn2 & syn3

& syn4 & !syn5

#!k1 & k2 & k3 & !k4 & !syn2 & syn3 & sy

n4 &!syn5

#k1 & !k2 & k3 &!k4 & syn2 &!syn3 & syn

4 & !syn5

#!k1 & !k2 & k3 & !k4 & !syn2 & !syn3 &

syn4 & !syn5

#k1 & k2 & !k3 & !k4 & syn2 & syn3 &!syn

4 & !syn5

#!k1 & k2 & !k3 & !k4 & !syn2 & syn3 & !

syn4 &! syn5

#k1 & !k2 & !k3 & !k4 & syn2 &!syn3 & !syn

4 & !syn5

#!k1 & !k2 & !k3 & !k4 &!syn2 & !syn3 &!syn

4 &!syn5);/** Logic Equations **/

EN=EN1&EN2

A1=!syn1 &!EN

A0=!syn0 &!EN

a=!A1&!A0& !EN

b=!A1&A0& !EN

c=A1&!A0& !EN

d=A1&A0&!EN

3.4 设置仿真向量

通过创建仿真测试文件TanShang.SI可进行仿真测试,当编译和仿真成功后,即可得到可下载到可编程逻辑器件的JED文件。该仿真测试文件Tanshang.SI如下:

ORDER:syn5,syn4,syn3,syn2,syn1,syn

0,k4,k3,k2,k1,OE,EN,A1,A0,a,b,c,d;

VECTORS:

00000000001LHHLLLH

00000100001LHLLLHL

00001000001LLHLHLL

00001100001LLLHLLL

从仿真结果很明显地可以看出:拨码开关的四位K1,K2,K3,K4分别代表00~0F(十六进制码)这16组,而每组的四个通道的输出为a,b,c,d;由于SYN0,SYN1,SYN2,SYN3,SYN4,SYN5可组成00~3F(十六进制码)共64个通道,从而实现了利用SYN0,SYN1,SYN2,SYN3,SYN4,SYN5分时选通64个通道回波信号的功能。由于EN始终为低电平信号,因此保证了AD8184的选通信号能够起作用。

4、结论

利用Advanced Protel PLD99的硬件描述语言CUPL进行PLD设计,具有设计简单、可操作性强的优点,在采用可编程逻辑器件进行系统设计时,由于其硬件描述语言CUPL能够定义内部逻辑和外接管脚的功能,而且在设计中根本不必考虑逻辑器件内部连线和组合逻辑阵列?Interconnect And Combinato-rial Logical?,再加上除了系统行为和功能描述外,所有设计过程都可以用计算机自动完成,所以,通过可编程逻辑器件?FPGA?等开发工具,在实验室就可以设计出专用的集成电路,从而真正实现电子设计自动化。由此可见:该方法并为数字系统的设计提供了非常方便的手段,灵活地解决了众多复杂的工程实践问题,从而可大大缩短研发时间。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多