作者:黄新财,佃松宜,汪道辉

1引言

数据采集是数字信号处理过程中的一个重要环节,已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤等领域。对不同的任务和应用场合数据采集系统要求的采样精度和采样速率各不相同,系统的实现方法和难度也各异。在低速数据采集领域,系统要求的采样速率低,数传输量小,系统的实现较容易,常用单片机系统完成数据采集、串行接口完成数据传输;在高速数据采集领域,系统要求的采样速率高、采集精度高、数据传输量大,于是系统的抗干扰、数据的传输、数据的存储问题就成了系统构建必须克服的关键问题。目前,常用的高速数据采集系统通常为定时采样或者固定采样门数据采集系统,这种系统数据采集的时间和数据量已知,待保存的数据都是被采样信号信息,通常通过设置足够大的缓冲区,通过PCI总线将缓冲区的数据传输到计算机内部总线,从而实现数据采集。

随着高速数据采集系统的发展,提出了变采样门连续高速采集的要求。此时系统不但要记录被采样信号信息,还要记录采样门的变化信息;由于采样门可变,采集的数据量变化、采样持续时间和采样的数据量不定,系统的实现难度较高。

本文提出了基于FPGA的四路变采样门的高速连续数据采集系统的实现方法。

2系统背景及功能描述

由于雷达重复扫描周期中,回波信号往往只占很小的时间部分。为了高效地获取回波数据,往往采用距离窗口推迟采样,以便滤除雷达重复周期中与目标无关的信号,提高数据有效率。因此系统触发信号、采样门、采样距离等都在变化。

本系统被测信号由四路雷达回波信号组成,基本要求:采样频率为20MHz;触发信号(triger)频率已知、可变(1KHz“2KHz);采样门(gate)为频率同触发信号、占宽比可变(5%”95%)。

3系统结构设计

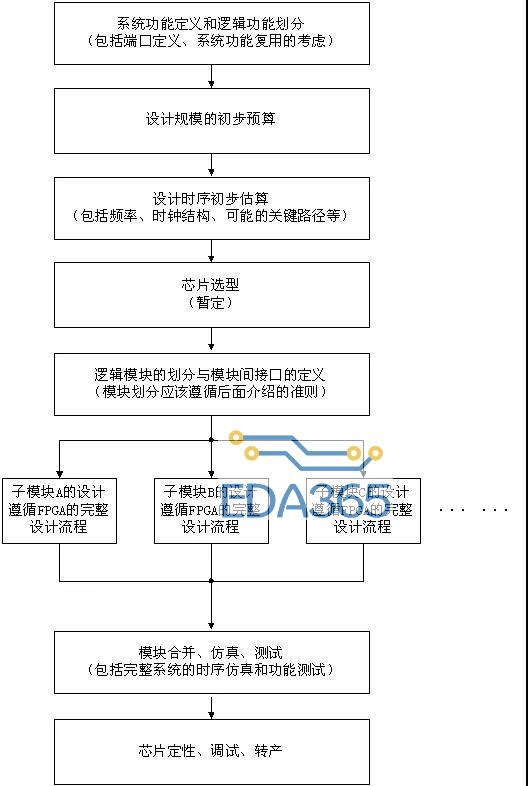

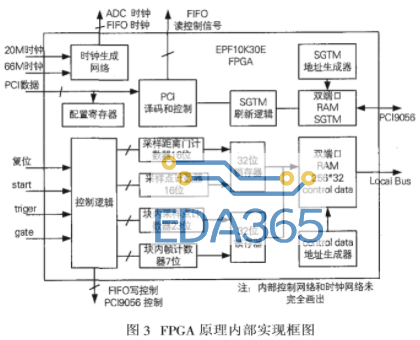

数据采集系统要解决的问题主要是数据的采集和传输问题。为了增强设计的灵活性和可扩展性,系统采用FPGA(FieldProgrammableLogicArray)来实现对AD转换器、数据缓冲器、时钟、数据传输的逻辑控制。

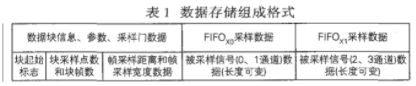

3.1术语定义和数据组织

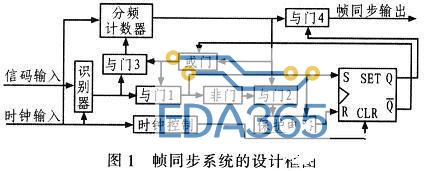

一个采样周期内的系统采集的数据称为一帧数据。系统设置的缓存能容纳多帧数据,当缓存存储容量不够存下一帧数据时就要转移数据,每次转移的数据称为一块数据。数据采集的目的是在信号发生后再现信号,所以为了便于数据回放(软件回放或者硬件回放),必须保存数据帧和数据块相关信息。系统保存的数据包括:被采样信号数据;采样门采样距离、采样宽度;数据帧、数据块相关信息。

3.2连续采集的实现策略

四路0“2V的模拟信号输入,由四个16位的A/D转换器完成模数转换,AD0和AD1构成一组32位的数据(A组),AD2和AD3构成另一组(B组)32位的数据。对于A组和B组数据,分别设置两个FIFO存储器FIFOX0、FIFOX1(X为A或B)。每组数据先暂存于FIFOX0,当FIFOX0的容量不够存储一帧数据时,FPGA控制数据流切换到FIFOX1,同时刷新SGTM表(DMA数据链指针表),启动PCI总线的DMA;先传送数据块信息和控制信息,然后传送FIFOA0数据,再传送FIFOB0数据,传送结束后DMA等待下一次传送。当FIFOX1容量不够存储一帧数据时,FPGA控制数据流切换到FIFOX0,同时控制逻辑刷新SGTM表,启动PCI总线的DMA;先传送数据块信息和控制信息,然后传送FIFOA1数据,再传送FIFOB1数据,如此反复采样和传送数据,从而实现连续数据采集。

3.3数据传输和存储策略

缓冲区的数据通过PCI总线以DMA方式传送到硬盘管理卡(SScard),该卡再将数据高速保存到硬盘阵列上。该系统硬盘阵列由8个40G硬盘组成(可根据需要扩展到16个硬盘)。PCI接口的实现方式通常有两种:通用FPGA实现方式和专用芯片方式。为了简化设计和提高系统的可靠性,本系统采用专用芯片方式。由于系统采用速率高,数据传输量很大,系统选用PCI9056芯片来实现PCI接口。该芯片支持66MHz/32BitsPCI总线,传输速率高达256M,支持数据链传输方式,便于实现大规模、多块数据传输[9]。本系统采用PCI9056的链式传送方式实现数据缓存到硬盘管理卡的DMA传送。为了发挥DMA的优势在FPGA上设置SGTM表。FPGA的控制逻辑通过对该表的刷新实时启动DMA操作。

4FPGA在系统中的应用

FPGA领域的快速发展使FPGA片上资源大量丰富,尤其使其高速性能和片上RAM使其特别适用于高速数据采集系统的设计。设计选用Altera公司的FLEX10K30E,该器件含有8个EAB(嵌入式阵列),每个EAB能够提供4K位存储位,每个EAB都有双口RAM实现能力;提供30000逻辑门;支持PCI总线,可提供66MHz的PCI性能;门级延时仅为6.5ns。本系统中FPGA设计主要包含时钟网络、双端口RAM、控制逻辑等。

4.1时钟及相关网络

时钟电路是高速时序电路设计的关键,本系统涉及20MHz和66MHz高速时钟,时钟是系统设计的一个重要内容。系统在一般逻辑控制和数据采集时采用20MHz时钟,存储电路工作在66MHz时钟下。为了提高时钟同步性能、系统工作频率和系统可靠性,设计采用如下措施:

1输入信号尽量通过锁存器;

2保证每路始终负载相当,以便减小时钟漂移;

3通过异步双端口存储器解决异步时钟匹配问题;

4大量使用有限状态机,提高设计的可靠性;

5大量采用流水线技术,提高系统工作主频。

4.2双端口RAM

由于FIFO的容量有限,每块数据包含的数据帧数有限,故必须在适当的时候进行数据切换。切换带来的块控制数据和对应每块数据的采样门计数器数据的数据量相对较小,设计通过设置了片上双端口RAM(controldataRAM),实现数据的缓冲。

因为系统采样速率高,数据传输量大,要求PCI响应快速,故本设计在FPGA上构造SGTM,PCI控制器一直查询SGTM,一旦发现SGTM传输控制字被置起,随即申请DMA操作,提高了PCI总线的DMA响应速度。

FPGA厂商提供的参数化模块库LPM(LibraryofParameterizedModules)中的双端口RAM模块都是只能一端读、一端写的双端口RAM。设计采用lpm_ram_dp模块再外加控制逻辑和仲裁逻辑的方法实现了两端都能进行读写操作的双端口RAM。每次数据切换时FPGA首先刷新SGTM,申请PCI总线进行DMA操作,DMA响应后首先传送双端口RAM的对应半区的数据,然后传输对应的FIFO上的数据。

4.3控制逻辑

控制逻辑实现对距离计数器、采样点计数器、块内采样点计数器、块内帧计数器等的控制;实现系统的设置和controldataRAM和SGTM的刷新;实现对FIFO的读操作、写操作控制和其它控制。

5应用和结论

本文提出了一种连续、高速、大容量、多通道的高速数据采集系统实现方案,并说明了该方案基于Altera公司的EPF10K30E系列FPGA的实现方法。目前本文实现的数据采集系统已经应用于某雷达数字信号处理系统中。经过实验室和室外测试,系统工作正常,达到了设计的要求。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多