引言

SPI(Serial peripheral interface——串行设备接口)是摩托罗拉公司推出的一种同步串行通信接口。用于MCU和外围扩展芯片之间的串行连接,现已发展成为一种工业标准 。一路SPI数据总线只占用3或4个I/O(Master Output Slave Input,MOSI; Master InputSlave Output, MISO;Serial Clock,SCK;Chip Select,CS)端口,可以简化电路设计,节省端口资源,提高设计可靠性 。SPI总线主要特点:全双工;可以当作主机或者从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。基于以上特点结合FPGA的特性,通过将SPI总线与FPGA相结合,可使SPI总线的应用更加灵活多变,为解决通信技术问题提供更好的选择和可行方案。

结合已交付的项目的经验(项目中主设备采用ARM芯片,从设备采用FPGA),探讨基于FPGA的SPI总线传输方案在实际中的应用,拓展SPI技术的应用范围,同时对设计中遇到的具体问题提出了有效的解决方案。

1、系统分析和设计

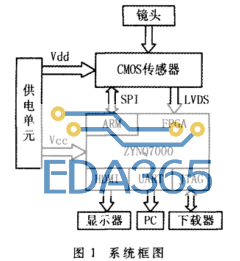

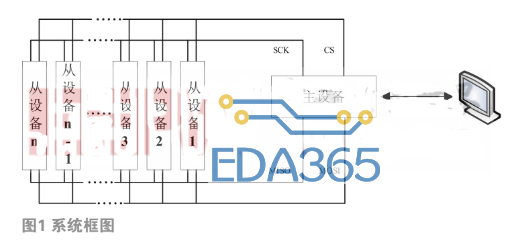

系统的SPI总线连接如图1所示。系统中的各从设备可以按照实际需要,实时采集不同的状态数据信息,并按SPI总线通信方式上报给主设备,主设备将最终的处理结果上报PC端,从而实现对系统的实时监控。

从设备需要采集的数据种类繁多,相对于使用单片机的单线程串行的工作方式来进行多种数据采集处理的工作方案,使用FPGA的工作方式显然是更优的选择(并行处理能力、运行速度快、管脚多、体积小,同时具有处理复杂问题的逻辑功能),从集成性、可靠性、兼容性等方面综合考虑,很明显最佳的设计方案就是从设备使用FPGA进行数据采集、处理。

主设备主要向从设备发送查询指令,同时将采集到的数据进行有效性判断并上传电脑。相对于从设备来说,主设备处理过程比较简单,选择较灵活、功耗低的ARM嵌入式最为合适。并且ARM具有现成的SPI接口驱动供开发者使用,大大降低了开发成本。

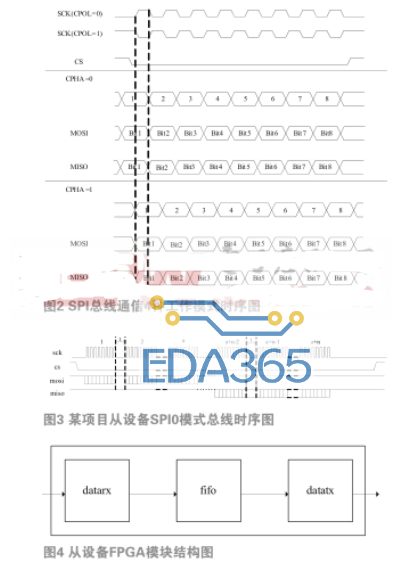

2、系统时序

时序是通信系统中首要考虑的因素之一,时序无误才能保证数据在传输、处理过程中的有效性,使系统保持正常的工作状态。根据时序的不同,SPI总线有4种工作模式(SPI0,SPI1,SPI2,SPI3),见图2,其中SPI0和SPI3两种工作模式使用的最广泛。通过配置系统的SPI总线的时钟极性(CPOL)和时钟相位(CPHA)可得到满足传输要求的工作模式。

当CPOL=0,串行同步时钟的空闲状态为低电平;当CPOL=1,串行同步时钟的空闲状态为高电平。可见,CPOL对于SPI总线传输协议没有较大的影响。

传输协议的模式选择主要通过配置时钟相位(CPHA)实现。当CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;当CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。确保SPI主、从设备之间的正常通信,就必须满足二者的时钟相位和时钟极性一致 [4] 。

现以某项目(采用SPI0模式)为例,选择其中1路SPI总线并对其时序进行详细阐述。时序图如图3。

片选信号cs在主设备发送数据前跳变为低电平,使被选中的从设备SPI通信端口开启;从设备完成数据发送的一段时间后,片选信号cs跳变回高电平,从设备SPI通信端口关闭。主设备发送查询/控制命令的数据帧长度为a个字节,每个字节包含8位有效数据,每位数据占用一个时钟脉冲信号;当有数据发送时,sck伴有对应的同步时钟信号,无数据发送则无时钟脉冲信号。同时,相邻字节间存在时间间隔t,在t时间内sck无时钟脉冲,即同步时钟信号是一份一份的,每份包含8个时钟脉冲。

因此,一帧完整的查询/控制指令,其数据中的每个字节占用8个时钟信号,主设备发送一条帧长度为a字节的数据需要8×a个时钟脉冲信号;假设从设备的缓存模块fifo和发送模块datatx完成对应的数据反馈过程所需最少时钟脉冲信号个数为8×n。为保证系统的通信功能正常,sck传输的时钟脉冲数应不少于该SPI总线完成一次查询/控制所需时钟信号个数(8×(a+n))。

3、技术难点及解决方案

3.1 数据同步

从图3的SPI时序图可看出,有数据才有时钟脉冲,总线的时钟不是连续而是一份一份的(每份为8个连续时钟信号),为了保证系统能正常通讯,必须确保数据在主、从设备中同步传输,这就增加了系统在数据传输过程中的难度。

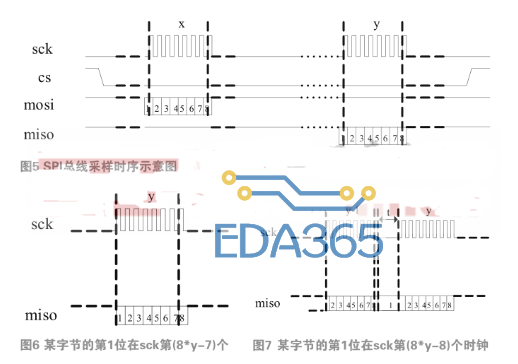

就从设备而言,必须满足从设备在接收/发送状态下,经过每一份时钟信号中接收/发送的都是的一个完整且有效的字节。即主设备发送数据的每个有效字节的第1位都是在第(8×x-7)个时钟信号(x为整数,0《x《a)被从设备的接收模块采样(上升沿采样,下同),然后依次采样直至该字节的最后一位在第(8×x)个时钟信号被采样。同时,要求主设备接收数据的每个字节的第1位都是在第(8×y-7)个时钟信号输出(y为整数,n》y》a),然后依次采样直至该字节的最后一位在第(8×y)个时钟信号输出完毕,如图5所示。

为了实现数据同步,可以采用如下方式:

(1) 从设备利用片选信号cs复位清零。通过片选信号cs的下降沿,触发从设备中的数据采集模块datarx、数据缓存模块fifo及数据发送模块datatx的计数清零,确保系统在片选有效后的第一个时钟脉冲开始计数,避免因计数错误造成数据采样失效。若采用第一个时钟脉冲进行计数清零,会使数据的采集滞后1位,以致采集到无效数据,造成通讯失效。

(2) 利用时钟信号sck计数。本文SPI总线采用SPI0工作模式,利用时钟信号sck的上升沿触发采集模块内部计数器计数,确保模块的数据采样同步,获得有效数据。

(3) 从设备中的数据发送模块datatx提前发送数据。

假设数据发送模块datatx在数据发送过程中,某字节的第1位在第(8×y-7)个时钟信号输出(y为整数,n》y》a,时钟信号的上升沿输出数据,下同),第八位在第(8×y)个时钟信号输出,那么将会出现如图6所示的情况。

由于总线采用SPI0工作模式,那么主设备将通过同步时钟信号的上升沿触发数据采集,此时采集到的数据正处于电平跳变中,以致主设备采集到不确定的无效数据。

结合图6可以发现,datatx模块通过提前发送数据,能有效的解决该问题,数据传输示意图如下。

当datatx模块在发送某个字节时,利用上一字节的最后一个时钟脉冲(第(8×y-8)个时钟脉冲)的下降沿触发该字节第1位的发送,第(8×y-7)个时钟脉冲的下降沿触发该字节第2位的发送,直至该字节第8位在第(8×y-1)个时钟脉冲的下降沿发送完毕。使用这种方法,主设备在每个sck时钟信号的上升沿都能同步采集到正确的数据,确保总线通信正常。

3.2 多个从设备并联的问题

笔者在调试过程中,系统连接板上只接入1台主设备和1台从设备,系统能正常运行。但在接入多个从设备后(从设备的接口类型一致),会出现一个或者几个从设备工作失效。具体表现为从设备没有任何信息反馈,且故障无规律可循:

a)与从设备插入插槽的位置没有特定规律。例如,有A、B两台从设备,连接板有5个插槽(编号1-5)。A插入1,B插入2,此时B失效。将B依次换至剩余插槽,可能会出现B失效、A失效,甚至两者失效的情况。然而,在A、B都能正常运行的情况下,互调A、B位置,也可能出现上述三种失效现象。或者将从设备B换成完全相同的从设备C,这种新的组合相较于之前A+B的组合,在接入方式完全相同的情况下又可能产生不同的结果。

b)与从设备的插入数量没有特定规律。连接板上从设备数量的增加或者减少,对整个系统的好坏并没有特定方向的影响。加上插槽位置对系统工作的影响也很复杂。

为了解决这个问题,笔者做过如下依次尝试,但情况并没有发生好转,从设备依旧没有任何信号输出:

a)将待机状态的从设备输出置高阻;

b)I/O设置上/下拉电阻;

最终笔者通过对设备内部的信号输入至信号处理部份采用SIGNALTAP进行实时分析、观察,发现数据处理模块fifo在固定位置丢失一个同步时钟脉冲(fifo的所有触发只与同步时钟sck有关)。经过分析,决定在fifo中加入异步时钟参与触发和计数,故障现象没有再次发生,多个从设备并联的问题得到了有效解决。

4、结论

利用ARM+FPGA模式搭建了SPI总线,使SPI接口技术的使用更加灵活多变,丰富了系统的I/O数量,增强了系统的数据处理能力,拓展了SPI技术的应用范围,实现了系统数据的长期可靠传输,为后端用户的决策提供了稳定可靠的理论依据。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多