1引言

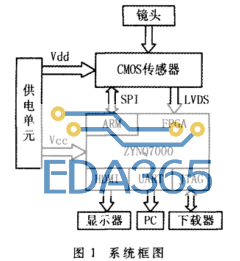

由于数字信号只有高电平和低电平两种情况,因此,用单片机(MCU)就可直接实现多路数字信号进行采集和逻辑分析。但由于单片机的时钟频率较低,完成一次采样的时间受程序执行指令速度的限制,采样速率通常不超过1MHz。因此,用单片机只能实现对低速率数字信号进行逻辑分析。FPGA的工作时钟速率通常可达200MHz以上,可对高速数字信号进行采样,但普通的FPGA在与外部设备进行数据交换时显得不灵活。为了解决上述问题,通常是将MCU与FPGA结合起来,用FPGA对高速数字信号进行采样,用MCU负责与外部设备进行数据交换,从而实现对高速数字信号进行逻辑分析,如图1所示。

图1逻辑分析仪框图

随着可编程逻辑器件的发展,Altera公司研发了可以嵌入软CPU核的Cyclone系列和StraTIx系列的FPGA芯片。嵌入式软核与普通硬核的昀大差别在于它的可裁减性,设计者可根据设计需求定制出不同结构的软核处理器。软CPU核的嵌入实现了CPU与FPGA的无缝连接,使芯片既能处理高速数字信号,又能方便灵活地与芯片外部设备进行数据交换,还增加了系统的集成度和可靠性。

2定制软CPU核

软核的定制要利用Altera公司提供的SOPCBuilder软件。

2.1定制NiosⅡ处理器

早期的软核处理器是Nios,但其稳定性不够好,现已被NiosⅡ所替代。

NiosⅡ处理器有三种类型:e(经济型)、s(标准型)和f(增强型)。选择不同类型的处理器所占用的逻辑资源和存储器资源大小不同,处理器的运算速度处理能力也有所差别。

2.2定制片内RAM

片内RAM作为软核程序的运行空间,对于没有扩展外部存储器的设计,片内RAM是必须的部分。通过软件设计向导,可以设置片内存储器的类型,大小,以及初始化文件。Cyclone系列芯片有13~64个片内RAM块,每个RAM块的大小是4K(128字×36位),用户可根据需要设置存储器的字数和字长。当定义的字数超过128时,多个RAM块可组成在一起,构成更大容量的存储器,满足设计要求。

2.3定制UART接口

UART接口是软核与计算机通信的主要接口,通过设计向导可定制UART接口。在定制UART接口时,可以设置其波特率,校验位,是否允许DMA控制。通过此基本设置,软核可以与PC机之间实现串口通信的功能。

2.4定制LCD控制端口和键盘控制端口

3最小系统形成

完成定制软核后,需要对软核编程,形成基于软核的昀小系统。

对软核的编程在NiosⅡIDE环境下进行。首先利用软件生成针对某软核的模版程序,用户程序都可以从模版开始。在生成模版程序的同时,也形成了system.h文件,此文件中包含了对用户编程有用的许多信息,包括所有端口的地址空间分配,中断号等。在文件altera_avalon_pio_regs.h中包含了对普通I/O端口进行读写操作的函数,通过对函数的调用可实现对端口的操作。在文件altera_avalon_uart_regs.h中包含了对UART操作的基础函数,对串口的所有操作,都可通过对此中函数的调用来完成。

在昀小系统中,实现软核对LCD的数据交换,读取键盘值,以及与计算机之间的通信。本设计键盘使用4*4键盘,显示器采用240*128点阵LCD显示模块。主要子程序流程图如图2所示。

图2键盘扫描和LCD控制程序流程图

4基于软核的逻辑分析仪设计

4.1总体结构

基于NiosⅡ的逻辑分析仪,采用FPGA硬件对数据采集和存储,NiosⅡ软核进行交互、控制和通信,并且可以通过LCD显示所采集数据的逻辑状态或通过RS-232接口与PC机通信,在PC上显示数据的波形并对数据长期存储。另外,通过键盘可对逻辑分析仪的采样频率、触发方式等参数进行设置,这些设置也都可以通过PC机进行。逻辑分析仪的整体结构如图3所示。

图3嵌入式逻辑分析仪总结构框图

4.2嵌入模块

4.2.1触发核模块

触发核主要决定什么时候采集数据,什么时候完成对数据的采集。在本设计中,触发条件分上升沿触发、下降沿触发、高电平触发和低电平触发四种。区分这4种触发信息至少要用到连续两个时钟的数据,因此每级触发条件有两个条件判断字,触发核通过两次比较判断是否触发。触发核是硬件核,由组合电路和触发器组成。

4.2.2PLL模块

在对数字信号进行采样时,需要的时钟频率至少应是数字信号波特率的5倍。Cyclone器件的嵌入式数字PLL要求外部输入CLK信号昀低频率不能低于20MHz,可通过分频的方式得到低频CLK,通过倍频的方式得到高频CLK,也可通过倍频和分频组合得到特殊的输出频率,本设计采用25倍频和2分频,使昀高时钟频率达250MHz。

4.2.3数据存储模块

由于软核在工作时也是在执行指令,运行速度不快,不能完成对高速数字信号的采集。为此,本设计在FPGA芯片中嵌入了FIFO,作为数据的缓存。所采集的数据,首先存入FIFO存储器中,这个过程全部通过硬件完成,每个采样时钟周期可完成一次数据的写入操作。当FIFO中数据写满时,存储器将通知软核读取数据,软核完成数据的处理、显示和传输等操作。

由于Cyclone器件中FIFO的容量不大,若采用固定的采用时钟,当输入数字信号的波特率较低时,FIFO存储的数据可能还不到一个码元宽度的数据,从而无法在LCD上显示其波形。因此,本设计采用了程控调整采样速率,从而保证了无论是低波特率信号还是高波特率信号,系统都能正确采样和显示波形。

4.3软核设计

软核作为设计的控制核心具有重要作用,为了完成对8路数据触发模式的设置,以及与PC机通信,在用SOPCBuilder软件定制软核时,为其加入了UART接口和若干位输入输出端口,这些端口也实现了通过键盘对各路数据触发方式和其它各参数的设置。

4.4软件设计

本设计编程语言采用的是C++++,软件流程包括参数设置、触发判断、数据采集、分析与通信、图形显示五个方面,主程序流程如图5所示。

图4逻辑分析仪工作流程

5结束语

本设计通过在Cyclone芯片中嵌入软CPU、数字PLL、FIFO和UART,实现了单片式8路高速数字信号分析仪。可用键盘改变采样速率,满足对不同速率的数字信号进行采样;用点阵式LCD显示所采集的8路数字信号;也可通过串口将采集的数据传输到PC机进行存储、处理和显示。本设计的时钟频率最高可达250MHz(CycloneⅡ芯片所支持的最高工作频率),从而可以对8路波特率为50Mbs的数字信号进行采集与显示。

图5PC机显示的8路数字信号波形

图5是通过嵌入式逻辑分析仪采集后,通过串行通信口送到PC机,在PC机屏幕上显示的8路数字信号实拍照片。

本文作者的创新点是:在Cyclone芯片中嵌入软CPU、PLL和FIFO.实现了CPU与FPGA的无缝连接。利用软CPU接收键盘的信息、驱动LCD和与PC机进行数据传输:利用芯片中PLL将低频时钟转换为高速时钟。并利用芯片中FIFO完成了对高速

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多