接触FPGA的朋友们都知道“复位”,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题。

常见的复位方式有三种

1、硬件开关:复位信号接一个拨码开关或按键,或者RC电路

2、电源芯片:上电时候电源芯片产生,可以长时间维持,直到稳定。

3、控制芯片:控制芯片产生复位脉冲。

复位管脚

理论上来说,FPGA器件是没有专用的复位脚的,任何一个通用IO都可以作为FPGA逻辑功能的复位输入。这一点与单片机不同。对于常见的FPGA开发板,可以使用按键来作为复位输入。例如在AC6102开发板上,有5个按键,任意一个都可以作为复位输入,而我们为了使用时的方便,使用右上角的按键作为复位按键比较方便,因为其离另外4个按键距离较远,设计功能时不易与其他按键混淆。用户也可以自行尝试将复位功能设计在另外4个按键上,也都是可以正常工作的。

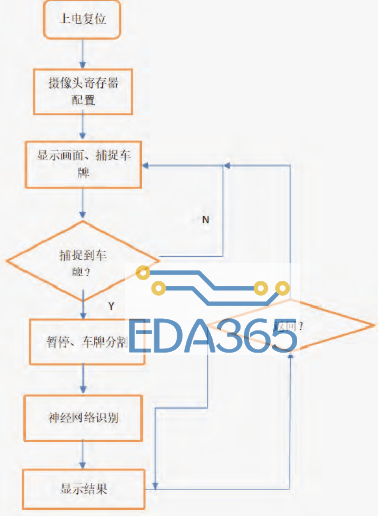

上电复位实现

既然上文已经说了FPGA上没有那个管教是专用复位脚,那么当使用某按键作为复位脚时,是否需要加入常见的RC复位元件,以支持上电复位呢?

实际上没有必要,其一是因为FPGA在完成配置之后有一个初始化过程,这个过程能对我们设置的reset管脚实现上电复位的类似功能。另外从严格意义上来说,FPGA逻辑代码是不能采用这样的常规上电复位思路的。原因在于fpga上电之后要首先进行配置流程,只有配置流程结束后,设计的逻辑功能才会开始运行。我们所说的复位脚,是针对正常运行时的逻辑来说的。然而,从上电到完成配置,最起码要0.5秒,一些大一点的FPGA器件,配置所需时间更长,可能长达几秒钟。一般的RC上电复位电路,时间也都在0.5秒以内,因此使用RC复位电路对于FPGA器件来说,实际上可能没有任何意义。即FPGA不能用外部延时复位电路,因为时间不够,FPGA逻辑还没就绪,上电复位状态就结束了。

对于fpga来说,要想实现上电复位非常简单,在内部设计一个计数器,计数满就释放复位信号并停止计时即可。这个在基础实验学习中可以不予理会。在后期复杂的系统设计中再行研究即可。使用按键作为复位输入更多是为了实现外部手动复位功能。

那为啥一般复位引脚会接在全局时钟引脚上?altera的寄存器有自动清零输入端口,用全局时钟可以让寄存器能够“同步”复位,这里的同步是大概同时到达的意思。因为全局时钟信号延迟低,抖动小,信号质量高。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多