为了满足市场对于更密集处理和提高系统整合度的需求,数字讯号处理功能已可运用于高效能平台组件上。全新的软件定义开发流程,让嵌入式软件设计人员更易于使用C/C++语言。

数字讯号处理是目前实现基本设备和服务所需的关键技术,这些基本设备和服务包含电信网络、行动通讯、数字音频、串流影音、工业马达控制与机器视觉、车载驾驶辅助、高效能雷达以及政府信息情报等。

为了满足更复杂的系统要求、降低延迟以及提高信道容量,专用的数字信号处理器(DSP)已经发展为传输率高达数十GFLOPS的多核心组件,可单独或以大型多DSP组合的形式使用。

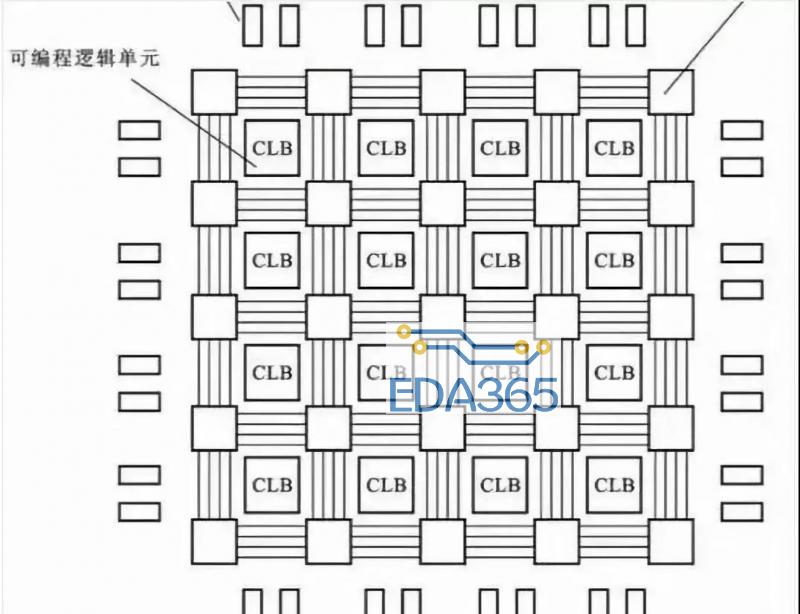

尽管如此,进一步发展的需求仍很大,设备设计人员正努力提高系统整合度以减少组件数量、强化可靠度,并降低成本。而为了满足相关要求,DSP扩展版本现可整合于多种平台,包括从ARM Cortex-M4小型嵌入式微控制器(MCU)至FPGA以及可编程系统单芯片(SoC)等。此外,当设计人员面对唯有透过高度平行化才能满足需求的密集处理,或如果系统需要高效能接口或客制加速器时,这些高效能的可配置组件现正成为理想选择。

新兴DSP平台

可配置SoC整合大量带有系统功能的DSP模块,包括处理器、内存、周边装置以及可编程逻辑组件等。例如,赛灵思(Xilinx) Zynq-7000 All Programmable SoC拥有多达2,020个DSP分割(slice),分别包括一个25x8的乘法器、48位累加器以及相关功能。此外,该芯片上还有一个双核心ARM Cortex-A9 MPCore应用处理单元、标准高速周边装置,包括USB 2.0、Gigabit以太网络,以及LPDDR2和DDR3等易失存储器接口。

另一方面,多核心处理器Zynq MPSoC可提供更多资源,包含多达3,528个DSP分割(每个分割包含一个27x18放大器)及外加PCIe Gen2、USB3.0、SATA 3.1和DisplayPort周边装置,并可支持DDR4易失存储器。而MPSoC架构也整合双核心ARM Cortex-R5 MPCore实时处理核心、四核心A53及ARM Mali-400 MP2绘图处理器(GPU)和H.264/H.265视讯编译码器。

Zynq-7000和MPSoC高效能ARM处理器还受益于高度整合的NEON多媒体加速技术、FPGA DSP分割、整合的周边装置,以及整合于UltraScale+ MPSoC中多达1143,000个逻辑单元。藉由上述资源,该组件能满足高度平行的处理以及支持广泛的系统整合需要,并超越传统多核心DSP水平。 对设计团队而言,现在正是超越大型多DSP开发板效能极限,让传统DSP跃升至All Programmable SoC平台的重大时刻。例如,利用这一技术,Xilinx的工程师协助了一家客户重新设计原来包含32个传统DSP芯片的雷达主板,而新设计的平台仅需两块可编程设计组件。

C/C++级硬件合成

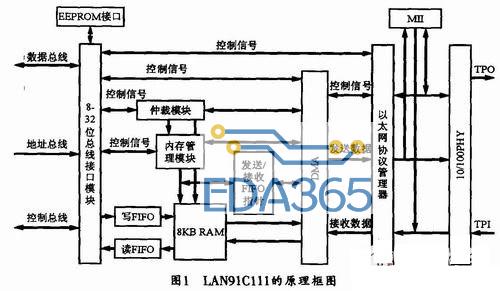

以往进行可编程FPGA和SoC设计时,工程师必须具备硬件设计技能来处理暂存级(RTL)设计,而这让原本掌握软件技能的设计团队无法充份发挥额外的功能和整合优势。图1显示简化软件开发以及效率和灵活度之间的权衡。图中比较传统软件可编程处理器以及在RTL或使用软件定义设计流程的可编程组件。

图1:软件定义流程让嵌入式软件开发人员充分了解All Programmable SoC组件的效能潜力

设计传统的DSP解决方案一直被视为是安全的解决方案。然而,随着高效能应用要求日益提升,高效能DSP的设计也越来越难以因应多核心架构的要求。因此,透过C/C++设计环境提供类似ASSP的程序设计体验,可协助系统和嵌入式软件工程师运用All Programmable SoC打造多处理系统。

类似ASSP的编程体验

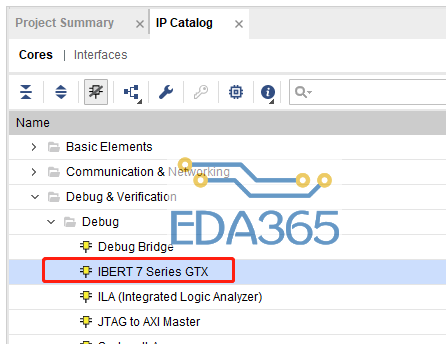

例如,赛灵思的SDSoC就是此开发环境的实例,软件工程师无需使用传统的FPGA工具或硬件设计语言(HDL),即可为可编程组件开发C/C++应用。此外,它也能妥善管理芯片处理、DSP资源,以及可编程设计硬件和内存,进而将系统效能最大化。

该环境包括系统级特性分析器,能在设计初期了解系统整体效能和功耗。图2显示特性分析器如何配合SDSoC流程。该特性分析器可快速估算系统效能,并指出哪些C/C++函数可透过可编程逻辑加速。SDSoC则随后透过编码报告软件周期、预估数据传输时间,并监控包含快取、内存和总线利用率等硬件应用情况。

该特性建立在赛灵思SDK的特性分析功能上,并在Zynq平台上执行完整设计的软硬件效能测量。快速估算工具则有助于使用者迅速评估一个或多个函数从软件转移至硬件所带来的效能影响,并使软件开发人员以此方式独立加速各个C/C++函数,从而避免软硬件团队间花费大量互动时间,并且能尽量减少可编程逻辑进行软件加速所需的迭代次数。相较于数小时或更长的硬件操作时间,这种方法仅需数分钟便可对修改所造成的影响进行评估。

图2:以PC样本为基础的非侵入性特性分析器

如图3所示,另一个C/C++全系统优化编译程序,主要针对SoC的ARM处理器和可编程逻辑及连接功能。此编译程序产生成的HDL程序代码,针对延迟、带宽及硬件利用率进行了优化。而系统级特性分析器与系统优化编译程序的结合,相对于以软件为核心而不采用硬件加速的解决方案,可提升整体效能至上百倍。

图3:全系统编译程序能控制效能、传输率和延迟,以减少设计反复的时间

拥有FPGA设计技术的系统架构师和平台开发人员可利用SDSoC的优势为嵌入式软件开发人员打造最佳应用平台。该工具利用自动化系统连接产生等特性,协助架构师快速了解Zynq处理系统、内存与可编程逻辑加速器间的最佳互连结构。

此外,架构师能利用赛灵思Vivado Design Suite的SDSoC打造特定应用的平台、配置如RTL描述等传统FPGA IP,并可作为可用的C语言函式库,进而实现重复利用以提高设计生产力。

软/硬件系统效能分析

工程师可利用SDSoC的追踪工具以了解其设计在选择不同工作负载、软硬件分割和系统设计下的执行情形。SDSoC Trace可提供详细的追踪说明图,包含应用在执行时的系统事件、执行在处理器、硬件加速器上的软件,以及系统内部的数据传输链接进行追踪。而相关事件以图形化的方式提供时间轴说明,且相对于事件记录,此追踪能呈现一定时间内的互动事件,并有助于进一步了解软硬件系统中的应用效能。

图4a显示SDSoC Trace如何自动在硬件系统中插入监控器;此外,追踪仪表也自动插入于软件系统中。图4b则展示软硬件追踪串流,以凸显出不同类型的事件。

图4a:SDSoC Trace启动后能自动插入必要的监控器和仪控功能

图4b:Trace可视化图形展示软硬件系统中的互动事件

开发板设计支持

藉由Zynq All Programmable SoC为基础开发板的ZC702、ZC706加上合作厂商和特定市场所提供的专用平台,如Zedboard、MicroZed、ZYB与影音和影像开发工具包等,SDSoC使软件工程和开发板设计可同时发挥效用。此外,每个开发板皆提供支持套件(BSP),可使SDSoC实现抽象平台的中介数据,为嵌入式软件开发人员和系统架构师提进一步提升生产力,并加速产品开发时程。

结论

结合ARM/NEON应用处理资源与大量DSP分割、FPGA架构的All Programmable SoC和MPSoC组件,可望使DSP效能超越目前的专用处理器。最新软件定义开发环境拥有让软件工程师能独立发挥新型组件的优势,同时为系统架构师与平台开发人员提供专家级的使用案例,使高效能讯号处理展现前所未有的简便。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多