随着社会经济的高速发展,由车辆大幅增加而带来的交通问题日趋严重。因此,作为交通监管系统的重要组成部分,交通信号灯在协调人、车、路的关系时发挥着巨大的作用。

EDA(Electronic Design Automation,电子设计自动化)是依靠功能强大的计算机,对以硬件描述语言HDL(Hardware Description Langu age)为系统逻辑描述手段完成的设计文件加以处理,自动实现既定的电子线路系统功能的一种技术。利用EDA技术进行电子系统设计的最终目标是完成专用集成电路ASIC(Application Specific Integrated Circuit)的设计和实现。ASIC作为最终的物理平台,集中容纳了用户通过EDA技术将电子应用系统的既定功能和技术指标具体实现的硬件实体。现场可编程门阵列FPGA(Field Programmahie Gate Array)是实现这一途径的主流器件,其特点是具有极大的灵活性和通用性,开发效率高,成本低,技术维护简单,工作可靠性好。

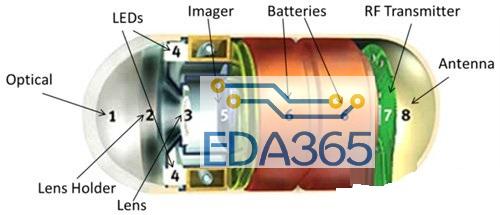

有一条主干道和一条支干道的汇合点形成十字交叉路口,主干道为东西向,支干道为南北向。为确保车辆安全、迅速地通行,在交叉道口的每个入口处设置了红、绿、黄3色信号灯及左转向灯,如图1所示。

(1)主干道绿灯亮时,支干道红灯亮,反之亦然,两者交替允许通行。主干道每次放行40 s,支干道每次放行30 s。每次绿灯亮,前10 s为左转灯亮,后5 s为黄灯亮。余下为直行灯亮。

(2)能实现正常的倒计时显示功能。

(3)能实现总体清零功能:计数器由初始状态开始计数,对应状态的指示灯亮。

对设计要求进行分析可知,主、支干道交通灯变化顺序应如图2所示。

状态转换如表1所示。

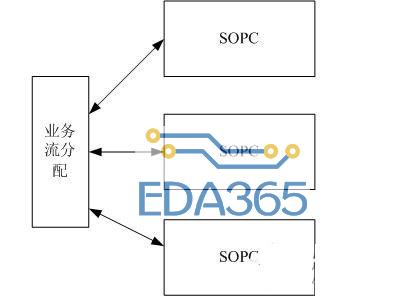

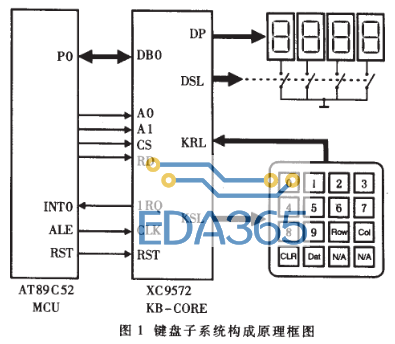

根据要求,系统结构图设计如图3所示。时钟脉冲由分频器对晶振脉冲进行分频产生。主控制器接收时钟信号,并据此进行状态转换,同时输出各状态的时间。信号灯控制器根据主控制器产生的状态量对主、支干道信号灯进行控制。由于主控制器输出的时间信号为实数类型,因此还需设计分位器将其转换为两组BCD码分别送至数码管显示。

为便于系统实现,采用VHDL语言对各个模块进行设计。主控制器为一计数器,输入信号为秒脉冲,以70为一个周期,计数到1后,在下一个时钟信号来到时,计数器复位,开始下一轮计数,如此往复。系统复位信号reset可使计数器从任意状态复位至状态S0,并重新开始计数。下面是主控制器的VHDL文件。其中clk和rst是时钟和复位信号,state表示当前状态,seg7a、seg7b分别表示主、支干道倒计时时间,temp为内置变量。

通过QuartusⅡ软件将各模块连接,进行编译、仿真,各模块可正常工作。分配引脚后,将配置文件下载至KX_7C5TP型FPGA开发板,系统运行正常,验证了整个设计的正确性,仿真结果如图4,图5所示。

从上述设计可以看出,利用FPGA进行交通信号灯控制系统的设计,使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件来完成对系统硬件功能的设计,这不仅提高了设计的灵活性,也便于设计者对信号灯的定周控制时间进行修改。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多