高扇出 net 是时序收敛的一个常见瓶颈。所以,除了传统的降低扇出的方法之外,还可以将该 net 引入 BUFG,但前提是有可用的 BUFG。众所周知,BUFG 是全局时钟资源,在配置 MMCM 或 PLL 时会用到。这里, 我就给大家介绍两种可以通过合理使用 MMCM/PLL 节省 BUFG 的方法。

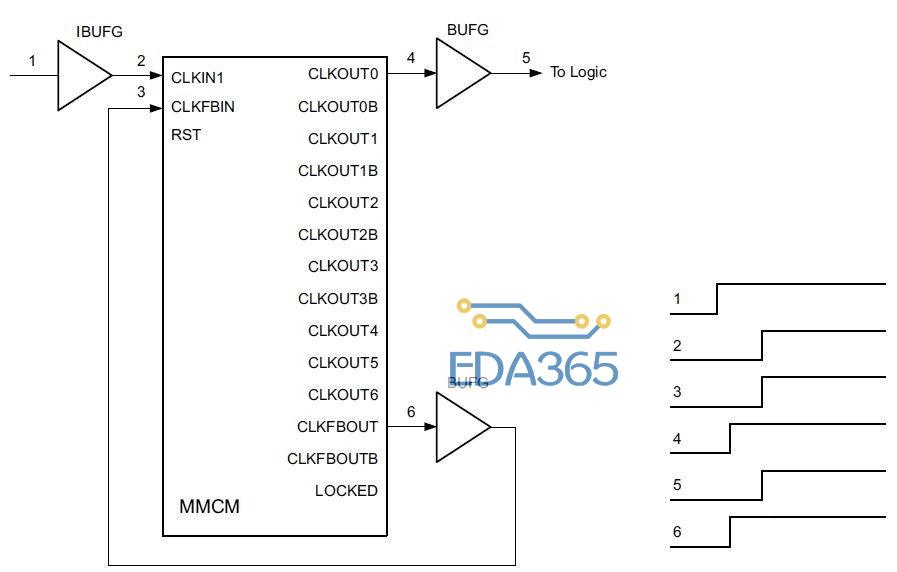

大多数情形下,MMCM 用作去除时钟网络 Skew 模式(Clock Network Deskew),如下图所示。在这种模式下,尽可能地合并同频时钟将是节省 BUFG 的有效方法之一。同频时钟可能来自于同一个 MMCM,也可能来自于不同的 MMCM。合并时需要考虑系统对时钟相位关系的要求。下图中,端点1、4、6为同相位,2、3、5为同相位。

注:图片来源ug572, figure 3-9

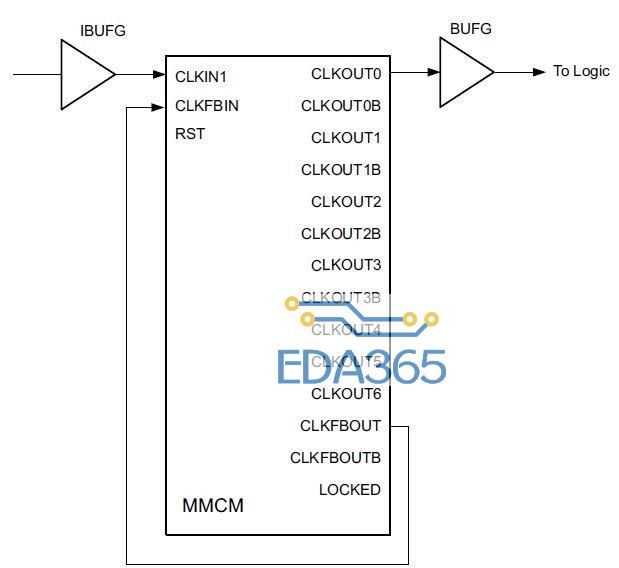

节省 BUFG 另一种方法,就是可以将 MMCM 工作在 INTERNAL 模式下。如下图所示。这种模式下,MMCM 被纯粹用作频率合成器,您无需关心 MMCM 输出时钟与输入时钟之间的相位关系。此时,CLKFBOUT 直接连到到 CLKFBIN,就可以节省一个 BUFG。

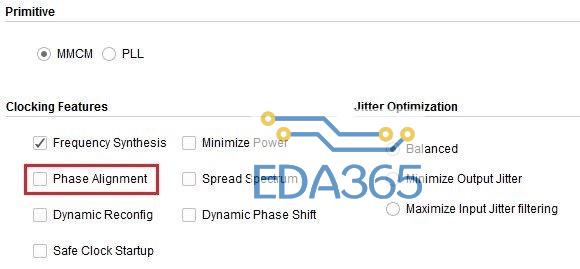

值得注意的是, 当你将 MMCM 用作 INTERNAL 模式时,对应于 IP Core中Phase Alignment 不勾选,如下图所示。

好了,这就是几个节省 BUFG 的非常有效的方法, 祝设计顺利。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多