出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序再对m序列进行CMI码型变换。在CMI码型变换过程中,采用专用寄存器对1码的状态进行了存储,同时利用m序列的二倍频为CMI编码进程提供时钟激励,最后输出CMI码型。实验结果表明,采用FPGA完成CMI编码的设计,编码结果完全正确,能够达到预期要求。利用这种方法实现CMI编码功能,具有效率高、可扩展性强、升级方便等特点,方便嵌入到大规模设计中,具有广泛的应用前景。

CMI码一般作为PCM4次群数字中继接口和光纤传输系统中的线路码型。这种码型不具有直流分量,有较多的电平跳跃,含有丰富的定时信息,因此很容易提取位定时信号,该码型具有良好的纠错能力,是一种很重要的码型。

在高次脉冲编码调制终端设备中广泛使用CMI码作为接口码型,在速率低于8 448 kb/s的光纤数字传输系统中也被建议作为线路传输码型。

本文主要介绍CMI码的编码具体实现方法,系统设计中采用了Altera公司CycloneⅡ系列的EP2C5Q型号FPGA作为系统的核心单元,完成CMI编码功能,程序设计平台为0uartusⅡ7.2软件,采用Verilog HDL作为程序设计语言。

CMI码的全称是传号反转码,CMI码的编码规则如下:当输入0码时,编码输出01;当输入1码时,编码输出则00和11交替出现,如表1所示。

根据此规则输出CMI码元的速率应为输入基带信号码元速率的2倍,对于输入为1的码字,输出不仅与当前码字有关,还与前一个1码的输出有关,1码对应的编码结果是00或11码型交替出现。由以上规则可以看出,在同步的情况下,输出只对应3种有效码型。即01、00、11码,而10码型则无效,因此可以根据这个特点进行检错。

设计中采用的是Altera公司的EP2C5Q型号FPGA,EP2C5Q是CycloneⅡ系列器件中的一种,CycloneⅡ器件采用90 nm工艺制造,在逻辑容量、PLL、乘法器和I/O数量上都较Cyclone有了很大的提高。EP2C5Q型号FPGA具有丰富的逻辑资源,共有4 608个逻辑单元(LE),26个M4K RAM块,2个PLL锁相环,13个18x18的乘法器模块。

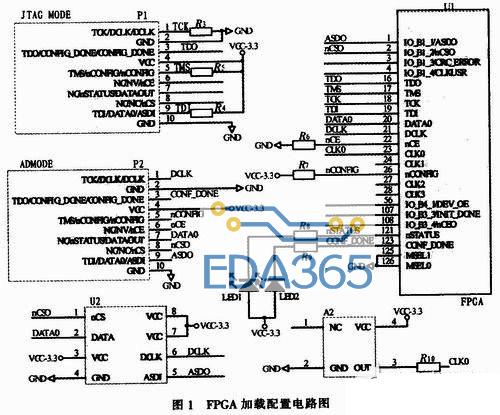

在FPGA硬件电路设计中需要注意的问题就是JTAG下载电路、配置芯片EEPROM电路与FPGA的连接关系。FPGA每次上电后都需要进行配置,从EEPROM中将数据读入,然后开始运行。根据FPGA在配置电路中的角色,其配置数据可以使用3种方式载入到目标器件中,分别是:FPGA主动(Active)方式;FPGA被动(Passive)方式;JTAG方式。在FPGA主动方式下,由目标FPGA来主动输出控制和同步信号(包括配置时钟)给Altera专用串行配置芯片(如EPCS1、EPCS4等),在配置芯片收到命令后,就把配置数据发送到FPGA,完成配置过程。要注意的是:Altera FPGA所支持的主动方式,只能够与Altera公司提供的主动串行配置芯片(EPCS系列)配合使用。这种配置模式只有在StratixⅡ和Cyclone系列(Cyclone和CycloneⅡ)的器件中支持。在被动方式下,是由系统中的其他设备发起并控制配置过程。比较常用的是JTAG配置方式JTAG是IEEE 1149.1边界扫描测试的标准接口。绝大多数的Altera FPGA都支持由JTFAG口进行配置,并支持JAM STAPL标准。从JTAG接口进行配置可以使用Altera的下载电缆,通过QuartusⅡ工具下载。

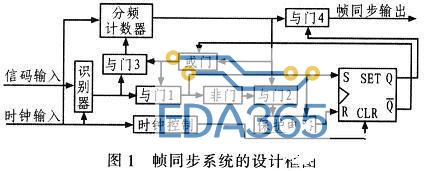

图1给出了FPGA的配置电路图,主要包括FPGA的主动(Active)方式和JTAG方式加载电路,以及专用串行配置芯片EPCS1与FPGA的连接关系。

在系统程序设计过程中,将m序列作为基带输入码,然后程序再对m序列进行CMI码型变换,最后输出CMI码型。通过对CMI编码规则的分析,1位输入码元对应2位输出编码,因此CNI码元输出速率是输入m序列码元速率的2倍。在程序设计中,要保持m序列进程时钟为CMI编码进程时钟的2倍频,这是完成CMI编码任务的前提。

m序列是最长线性反馈移存器序列的简称,m序列具有平衡性、游程特性、线性叠加性、自相关特性和伪噪声特性,应用十分广泛。设计采用m序列产生器产生的m序列作为CMI编码的数据源,用4级移存器构成周期为P=24-1=15的m序列发生器。m序列发生器的结构图如图2所示,其中A0、A1、A2、A3分别代表一个寄存器。

在对m序列进行CMI编码的程序设计时,要注意的问题是,1码对应的输出是与前一个1码的状态有关,因此要对1码的状态进行记录,从而实现1码对应的00和11码型交替输出。

CMI编码系统设计软件环境采用的是QuartusⅡ软件平台,QuartusⅡ是一种综合开发工具,它集成了Altera的FPGA/CPLD开发流程中所涉及的所有工具和第三方软件接口。通过使用此综合开发工具,设计者可以创建、组织和管理自己的设计,主要包括设计输入、综合、布局布线、时序分析、仿真、编程与配置过程。QuartusⅡ支持多时钟定时分析,内嵌SignalTapⅡ逻辑分析器、功率估计器等高级工具,易于管脚分配和时序约束,具有强大的HDL综合能力。

SignalTapⅡ逻辑分析器是很重要的测试工具,它是对FPGA的硬件信号进行读取,可以捕获和显示FPGA内部的实时信号行为,从而能够让设计者直观的判断出逻辑是否准确。SignalTapⅡ的功能类似于逻辑分析仪,但与传统的逻辑分析仪相比,具有如下优点:使用SignalTapⅡ逻辑分析器不占用额外的I/O管脚,若使用传统的逻辑分析仪观察信号波形,则必须将待观察信号引到空闲管脚;SignalTapⅡ逻辑分析器不占用PCB上的空间,若使用传统逻辑分析仪,需要从FPGA器件上引出测试管脚到PCB上,这样增加了PCB走线难度;SignalTapⅡ逻辑分析器还不会破坏信号的完整性;SignalTapⅡ逻辑分析器集成在QuartusⅡ软件中,无需另外付费,而传统的逻辑分析仪则价格昂贵。

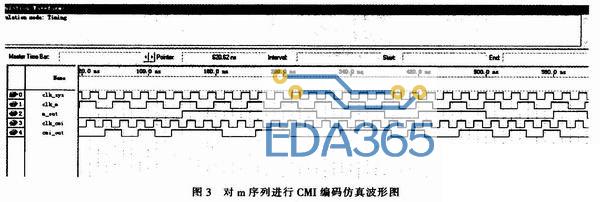

利用QuartusⅡ7.2软件平台对CMI编码程序进行了编译和仿真,通过仿真得到了编码仿真结果,图3给出了CMI码编码仿真波形。

从仿真结果可以看出,系统在时钟clk_m的触发下,由m_out寄存器输出m序列,输出15位的m序列值,依次为000111101011001;系统在时钟clk_cmi的触发下,完成CMI编码功能,而CMI编码后的输出值则由cmi_out寄存器输出,从仿真波形图上可以看出,CMI编码的码元输出速率是m序列码元速率的2倍。对应的输出值依次为010101110011000111010011010100,对应的CMI编码信号与m序列相比,有一定时间的延时,但编码结果完全正确。

本文详细介绍了采用Altera公司的FPGA,利用Verilog HDL语言进行设计的CMI编码系统的具体实现方法,Altera公司的CycloneⅡ系列EP2C5Q型号FPGA具有丰富的逻辑单元,通过QuartusⅡ软件的综合仿真,可以看到程序的设计仅仅占用了11个LE,占用FPGA的LE资源还不到1%。通过以上仿真结果可以看出,编码的结果完全正确,本文阐述的设计方法是合理的。

本系统的创新点是将FPGA应用于CMI编码逻辑的开发中,使系统设计简单,配置更灵活,易于扩展,摆脱了基于专用芯片设计的限制,系统采用FPGA作为CMI编码的核心单元,应用Verilog HDL对CMI编码逻辑进行描述,利用SignalTapⅡ工具对系统逻辑进行分析,具有开发周期短、成本低、效率高、升级方便等特点,系统还研究了4级移存器周期为15的m序列发生器的设计方法,这为CMI编码器的测试提供了信源基础。存在的问题是系统在设计时未能合理的选择FPGA型号,导致FPGA资源使用不尽合理,因此,在基于FPGA的系统设计过程中,为了避免产生资源浪费,一定要在设计前通过仿真手段大致的估算出设计需要的资源数量,然后选择相应的FPGA型号;但同时也要注意FPGA的容量选择要留有一定的余量,因为在大规模设计中,还可以将本文设计的CMI编码电路与其他功能模块都集成在一块FPGA中,这一点在CMI编码作为系统设计的一部分时便显得尤为重要。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多