FPGA全称是“可编辑门阵列”(Field Programmable Gate Array),其基本原理是在芯片内集成大量的数字电路基本门电路,存储器以及互连线资源,而用户可以通过对FPGA进行“编程”(烧写配置文件)来定义这些门电路的功能以及模块之间的连线。这种“编程”不是一次性的,你可以把FPGA设计成一个编解码器,只要更改配置文件,就可以变成一个CPU,这也是所谓的re-Configurable的概念。当然,FPGA在给我们提供了随意实现硬件电路的灵活性的同时,也要求设计者具有硬件设计的知识和能力。这一点和CPU,GPU的软件编程方法有很大的差别,或者说是有更高的应用门槛。

目前主要的FPGA芯片厂商是Xilinx和Intel(Altera),AWS主要使用Xilinx的FPGA,MS则使用Intel的FPGA。在具体看FPGA的内部结构之前,我们还是通过对比来看看它的特点。

其实最近这种对比很多,我之前的文章也提到过。MS把CPU,GPU,FPGA和ASIC放在Flexibility VS Efficiency的角度进行对比,这个也是我们经常使用的方法。再次强调,灵活性(通用性)一定意味着效率的损失,反之亦然。

认为FPGA主要还是用在Evaluation(或者我们经常说的Inference)。而有趣的是,他们认为ASIC方案在Training和Evaluation中都还是“under investigation”,好像把Google的TPU给忘了。

AWS给出了另外一个视角的比较,CPU为了实现最大的灵活和通用,芯片中的很大一部分芯片面积用来提供控制功能(也包括复杂的存储架构,比如Cache);而在GPU当中,用作运算的芯片面积比例大大提高,能够支持大规模的并行处理;而到了FPGA,已经没有预先定义的指令集概念,也没有确定的数据位宽。这些你都可以根据应用来自己设计。你可以设计一个只支持几条指令的处理器;也可以只设计数据通道和简单的控制逻辑,根本不用指令。

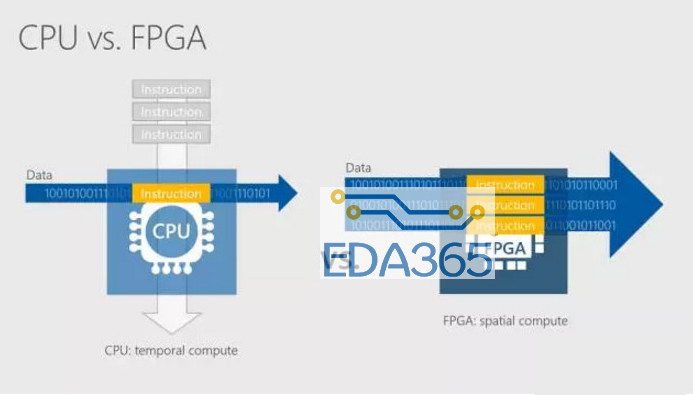

下图来自MS的讲座,对比了CPU和FPGA进行数据处理的特点。

CPU可以看作是一种时间计算模型,指令顺序进入,每条指令处理一定的数据。FPGA可以看作是空间计算模型,大量数据可以并行的进行处理。Deep Learning的处理,比如CNN的卷积运算,就是非常适合空间计算模型的例子。这一点我在之前的文章“深度神经网络的模型·硬件联合优化”中已有介绍。下面我们具体看看FPGA的内部结构。

FPGA中几个比较重要的基本模块包括(按照Xilinx的说法):

CLB(Configurable Logic Block):FPGA最基本的组成单元,可以实现基本的组合逻辑和时序电路。其中,LUT(Lookup Tables)是实现组合逻辑的部分,可以实现n个输入的任意组合逻辑运算(不同型号的FPGA有所不同,下图的例子中为6个输入)。而在CLB的输出位置,还有一个寄存器,提供时序电路的功能。

DSP Slice:是比CLB粒度更粗的运算单元,直接实现乘法,累加等功能。它比较类似与我们在DSP处理器中使用的MAC单元,如下图所示:

此外,一般FPGA中还提供片上Memory模块(Block RAM,UltraRAM),各种高速接口,IP和很多辅助电路。根据应用需求不同,有的型号的FPGA本身也是一个SoC,还集成了处理器核(比如ARM),甚至视频编解码等功能。在这里,我们观察CLB Flip-Flops,CLB LUT和DSP Slices的数量,以及memory的数量,基本就可以了解该FPGA的规模,也就是在这个FPGA上可以实现多大规模的数字电路。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多