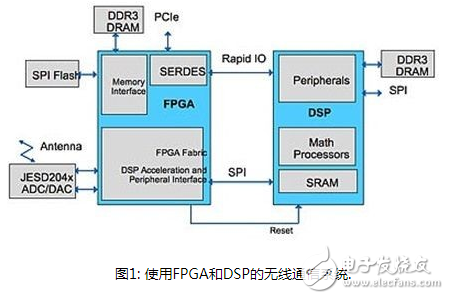

Altera推出40Gbit/s以太网路(40GbE)和100Gbit/s以太网路(100GbE)矽智财(IP)核心产品。这些核心能高效率的建构需大传输量标准以太网路连接的系统,包括晶片至光模组、晶片至晶片及背板应用等。

Altera媒体存取控制(MAC)和实体编码子层及实体媒体附加(PCS+PMA)子层IP核心符合IEEE 802.3ba-2010标准要求,降低用户在Altera 28奈米(nm)Stratix V现场可编程逻辑闸阵列(FPGA)和40nm Stratix IV FPGA中整合40GbE和100GbE连接的设计复杂度。

Altera企业和产品市场副总裁Vince Hu表示,越来越多的系统设计使用高速以太网路,不仅是区域网路附加子层,而且还有系统内部的互联。因此,包括40GbE/100GbE MAC和PCS+PMA层在内的子系统IP,成为系统设计团队工具套件的关键组成。

Altera这些核心针对Altera开发套件和Altera Quartus II软体12.0版整合进行最佳化,适用于在Stratix IV和Stratix V FPGA中开发高性能、低成本子系统IP。透过这种开发方式,Altera支援40GbE/100GbE系统级传输量,提高FPGA设计人员的设计抽象层级,同时提升设计团队的效能。

40GbE及100GbE MAC和PHY IP核心提供的介面,包括一个采用资料套件的通道,与前一代以太网路系统在逻辑上相容。资料速率高达28.05Gbit/s和14.1Gbit/s,并具有收发器的Altera Stratix V GT和GX FPGA,以及资料速率达达到11.3Gbit/s的Stratix IV GT FPGA都支援这些核心。Stratix FPGA结合高密度、高性能及丰富的特性,支援用户整合更多的功能,提高系统频宽。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多