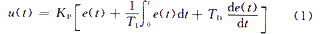

摘 要: 为解决粗粒度密码逻辑阵列控制开销大、控制效率低的问题,在研究主流阵列处理架构下三层控制模型的基础上,提出了一种阵列的四层控制模型,并设计了对应的可编程控制网络。在规模为4×4的可编程控制网络上实现了对AES、A5-1等对称算法的控制流映射。在65 nm CMOS 工艺下,DC综合结果显示总面积为13 712 μm2,折合等效与非门数0.95万,占阵列面积0.37%。映射AES和A5-1控制流最高频率分别为1 389 MHz和1 190 MHz,达到面积小、速度快的应用需求。将四层控制模型与三层控制模型进行六个不同性能对比,前者整体性能远超后者,且能满足任意网络互连结构阵列的高效控制需求。

引言

网络带宽的增长和网络安全协议的多样化,导致密码应用不断扩大及对密码设备性能要求不断提高。对于运算密集型的密码算法,数据流驱动的粗粒度密码逻辑阵列(Coarse-Grained Cryptographic Logic Array,CGCLA)结构可充分利用其数据并行性和算法流水的特性,达到密码运算速度快、灵活性高等性能要求。然而面对如此灵活高效的可重构数据通路,若阵列控制器控制效率低,延迟和面积大,则控制时间开销与数据路径时间开销相当,因此控制路径可能成为关键路径,将导致成本高、扩展性差等问题,所以高效率的控制器将成为CGCLA发挥其良好性能的关键。

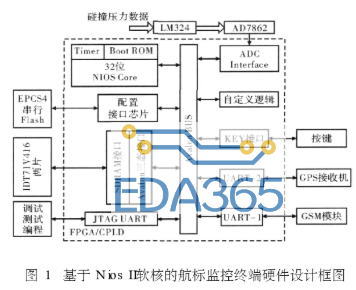

本文对3种主流可重构处理架构的控制模式进行研究,发现ADRES架构的控制器存在面积规模大、可扩展性差等问题;XPP架构下控制范围存在局限性、控制流间信息交互难等问题;MorphoSys架构下控制流单一,且存在交互开销和存储开销大的问题。针对以上架构存在的控制缺陷,从对称密码算法结构出发,提取控制流特征,采用了全动态的配置信息技术,提出了一种性能强大的四层控制模型,并设计了在该模型下面向CGCLA的可编程控制网络结构,克服了控制器可扩展性差、交互时间长、信息交互难、控制流单一、映射算法困难等问题,从而能很好地支持对分组密码算法和序列密码算法的高效控制。

目前,可重构密码处理架构主要有两种:阵列结构(ADRES[1]、XPP[2]、MorphoSys[3]、S-RCCPA[4]等)和VLIW结构(Cryptonite[5]、CCproc[6]、RCB-CP[7]等)。对于实现运算密集型密码算法,阵列结构数据加速、资源利用率等性能更优。

ADRES架构由超长指令字处理器控制,属于集中控制方式,能做到配置信息的周期级切换,但是超长指令字处理器定制性太强,导致面积规模大、可扩展性差等问题。XPP架构的控制模式属于半集中式控制,每个阵列处理簇能产生至少一个控制流,通过配置页面切换,能实现比ADRES架构更为灵活的控制,然而当需要数据流图或控制流图交互时,此架构不能实现或者实现效率很低,从而可能造成算法映射困难、配置管理器间交互开销大等问题。MorphoSys架构由于只有单一的主处理器控制阵列,只能产生单一的控制流,对于多种密码算法的并行实现适配效率非常低,降低了阵列数据并行性的优势,而且存在控制与运算交互时间长、局部存储开销大等问题,所以不能实现高效控制。

将以上3种主流架构的控制模型抽象成三层,如图1(a)所示,对其进一步改进,抽象成四层控制模型,如图1(b)所示。在配置页面层与可重构阵列之间,加入可编程控制器,控制器能够接收各个处理单元的反馈信息,并根据反馈信息选择配置页面,增强了数据流与控制流间信息交互能力,可以提高控制效率,但仍然存在可扩展性差、控制流单一等问题,且此种基于阵列的配置技术在配置页面切换时会产生巨大功耗。

对四层控制流模型进一步改进,如图1(c)所示。控制层采用基于网络互连结构的控制网络设计,为每个处理单元分配一个能产生简单控制流的可编程控制器(Programmable Control Element,PCE),然后结合三维配置信息技术[8],为阵列的每个处理单元分配存储空间来存储算子配置信息,改进后的四层控制模型通过可编程控制器网络互连可以产生不同或者复杂的控制流,通过三维配置信息技术能够完成全动态配置,且能克服基于阵列配置技术带来的页面切换功耗大的问题。

为设计合适的粗粒度密码逻辑阵列可编程控制器,就必须从对称密码算法的结构特征出发,总结提取合适的控制方法。

2.1 数据流复用控制

无论是分组密码算法的轮运算、序列密码算法的记忆部件更新,还是杂凑算法消息扩展运算和轮运算,都满足迭代原则,其数据流呈现很强的规律性:每次运算都使用了完全相同的数据流,每组中间数据都只与下一组数据直接相关。

2.2 不等长数据路径控制

分组和杂凑密码算法在一个分组内需要计算多路数据,如图2(a)所示。而每一路数据可能需要不同的操作,操作数据也有可能不同,为保证得到正确的计算结果,一般有两种可行方案,第一种是在较短的路径中插入无效操作使其与较长路径等长,如图2(b)所示。在路径较多的情况下,该方式变得很复杂,且浪费资源。第二种是通过不断向自身赋值的方式保持原值不变从而使较短的数据流停止,如图2(c)所示,等到另一数据算出正确结果后再切换到下一数据流图进行运算,即原来的一张流图将被拆成两张子图,然而杂凑算法内部一般存在很多路数的运算,所以不适合采用第二种方式。在此,基于第二种用子图切换实现等待的方式,提出一种寄存器等待的方式,如图2(d)所示,通过使能寄存器,达到不同路径的同步。相比前两种方式,提高了资源利用率,也减少了子图的数量,从而可以减少控制复杂度。

2.3 切换控制

对称密码算法一般由多个执行不同运算的阶段组成,相应的对称密码算法全局数据流图一般由多个不同的子图构成。分组密码算法可分为初始运算、轮运算、输出运算3个阶段,序列密码算法大致可分为密钥输入、记忆部件初始化和置乱输出3个阶段,而杂凑算法的每一轮采用的是完全相同的运算结构,一般不存在阶段划分。

2.4 钟控、控选结构控制

与分组密码算法任意时刻有确定的数据流图不同,序列密码算法由于钟控模型的存在,导致数据流有不确定性,这就要求在运算中临时确定数据流图,满足此要求一种方法是采用选择结构,同时实现两路钟控运算,相当于将控制流整合至数据流中,使其也同样具有固定的数据流,代价是需要更多的资源,运算变得更加复杂。另一种方法是将计算钟控值所需的抽取位传递至控制流,控制流根据抽取位决定数据流图选择,如图3所示。这种方法资源变少、运算简单,但控制流与控制流关系更加复杂。

针对主流架构存在的控制问题,本文提出了可编程控制网络。用网络结构解决控制器可扩展性差的问题,用紧耦合方式克服交互时间长的缺陷,用互连方式解决信息交互难、控制流单一、映射算法困难等问题。

3.1 双层网络交互结构设计

双层网络包括可编程控制网络和用于数据处理的数据网络。紧耦合的双层网络交互结构如图4所示,其紧耦合主要体现在基本控制单元(Control Unit Cluster,CUC)与基本运算单元(Basic Processing Unit,BPU)之间存在一对一的耦合方式。该耦合方式通过硬连线实现,最大程度地减少了控制与运算交互时间,可以快速实现BPU配置页面切换,且不占用互连资源。

3.2 可编程控制网络互连结构设计

可编程控制网络是一个五向节点结构的网络,其结构如图5所示。主要包含了两个功能模块:可编程控制器PCE和路由单元SE(一个CUC包含一个PCE和一个SE)。其互连拓扑结构是由路由单元SE通过规模为4×4的2D Torus网络互连构成。每个可编程控制器PCE可产生一个简单的控制流,PCE通过SE互连,可以形成更多更复杂的控制流,然后与数据流完成整个算法在阵列上的映射。

3.3 可编程控制器PCE结构设计

可编程控制器PCE功能的设计需依据对称密码算法控制流特点。基于功能的完备性考虑,根据第2章对对称密码算法研究得出的控制方法进行分析,得到可编程控制器PCE的功能需求,如表1所示。根据PCE功能需求,可以推出对应的基本功能组件,如表2所示。

从表1、表2可知,本文提出的可编程控制器PCE必须具有5种基本功能组件,即计数、比较、布尔运算、值传递以及状态寄存,以很好地支持对称密码算法控制流映射。可编程控制器PCE结构如图6所示。

4.1 功能验证

4.1.1 AES算法控制流映射

本文选取密钥长度为128 bit、轮数为10轮的AES算法进行分析,根据AES算法结构和迭代型运算特点,对其进行数据流子图划分,子图1实现开始的异或运算,子图2实现1~9轮运算,子图3实现第10轮运算。

根据子图切换条件及切换顺序,选择基本功能组件完成AES的控制流映射,如图7所示,分别用到了计数器、比较器以及子图选择信号的值传递等基本功能组件,密钥的读取地址通过轮计数器产生。

4.1.2 A5-1算法控制流映射

根据是否输入密钥将整个A5-1数据流图分成2个子图,子图1完成带密钥运算的86次初始化操作,子图2完成之后的2轮100次空转和114次置乱输出。根据子图切换条件及切换顺序,选择基本功能组件完成A5-1的控制流映射,如图8所示,分别用到了计数器、比较器、布尔运算(LUT)以及子图选择信号的值传递等基本功能组件。

4.2 性能分析

本文使用Synopsys公司的DC(Design Complier)工具,采用65 nm CMOS 工艺标准库在tt_vlp2_25c的PVT环境下对规模为4×4可编程控制网络进行逻辑综合。综合报告显示,可编程控制网络占用组合逻辑面积为12 256 μm2,非组合逻辑面积为1 456 μm2,总面积为13 712 μm2,折合等效与非门数 0.95万门(13 712/1.44门),占整个CGCLA面积0.37%。映射AES控制流最大延迟为0.72 ns,即频率达到1 389 MHz。映射A5-1控制流最大延迟为0.84 ns,即频率达到1 190 MHz。从综合结果可以看出,可编程控制网络面积小、速度快,不会增加阵列面积资源或成为关键路径。

其次,将四层控制模型下的可编程控制网络与三种主流架构下的控制器进行性能对比分析,结果如表3所示。可编程控制网络整体性能远远优于主流架构下的控制器,不仅可以提高了控制效率,且在关键配置技术上提供了很好的技术支持。

为了解决当前主流密码阵列架构下控制器可扩展性差、控制流单一、与数据流交互时间长等问题,本文提出了四层控制模型,并设计了面向粗粒度密码逻辑阵列的可编程控制网络。用AES和A5-1算法在控制网络上映射,对其进行功能验证和性能分析,结果表明,可编程控制网络不仅支持分组密码算法控制流映射,还支持序列密码算法控制流映射,且面积小、延时少,灵活性和扩展性也很高,达到高效控制且开销小的设计要求,适用于任意互连结构的粗粒度密码逻辑阵列。与3种主流阵列处理架构进行六方面的性能对比,发现基于可编程控制网络的四层控制模型整体性能远超三层控制模型。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多