摘要:分析了PCI 9054芯片的性能,讨论了利用PCI 9054本地总线扩充FIFO的方法。并以IDT72205 FIFO为例,给出了具体的设计方案。

关键词:PC总线 PCI接口芯片9054 FIFO

PCI总线是Intel公司推出的一种高性能局部总线,其数据总线为32位,且可扩展为64位,最大数据传输速率为132~264MB/s,是目前使用非常普遍的一种总线。因PCI协议比较复杂,较难掌握,故PCI总线扩展卡的开发校ISA总线等其它扩展卡难度大。PCI 9054芯片是一种能满足PCI V2.2协议,特别适用于PCI总线外设产品开发的PCI→本地总线I/O加速器芯片。

1 PCI 9054性能

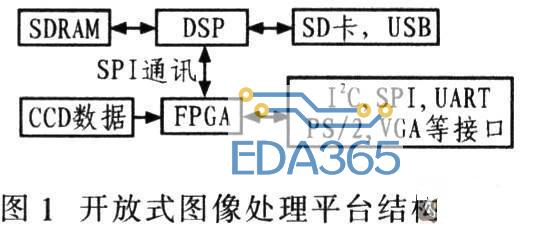

PCI 9054是美国PLX公司生产的先进的PCI I/O加速器,其内部框图如图1所示。它采用了先进的PLX数据管道结构技术,是32Bit、33MHz的PCI总线主I/O加速器。

PCI9054主要特性如下:

·符合PCI V2.1,V2.2规范,包含PCI电源管理特性。

·支持VPD(Vital Product Data)的PCI扩展。

·支持PCI双地址周期,地址空间高达4GB。

具备I2O准备报文单元,完全兼容I2O V1.5规范。

·提供了两个独立的可编程DMA控制器,每个通道均支持块和Scatter/Gather的DMA方式,DMA通道0支持请求DMA方式。

·在PCI启动模式下,PCI 9054可插入类型1和类型2的配置周期。

·PCI←→Local Bus数据传送速率高达132MB/S。

·支持本地总线直接接口Motorola MPC850或MPC860系列、Intel i960系列、IBM PPC401系列及其它类似总线协议设备。

·本地总线速率高达50MHz;支持复用/非复用的32bit地址/数据;本地总线有三种模式;M模式、C模式和J械,可利用模式选择引脚加以选择。

·具有可选的串行EEPROM接口。

·本地总线时钟由外部提供,该时钟可和PCI时钟异步。

·具有8个32bit Mailbox寄存器和2个32位Doorbell寄存器。

·两种封装形式:176引脚的PQFP和225引脚的PBGA封装。其引脚信号分为4类:电源、地引脚;串行EEPROM接口引脚;PCI系统总线接口引脚;本地总线模式及处理器独立接口引脚。

PCI 9054内部有6种可编程的FIFO,其长度如表1所示,以实现零等待突发传输及本地总线和PCI总线之间的异步操作。

表1 PCI 9054内部FIFO

| FFIFO | 长度 |

| PCI启动I/O读 | 16长字 |

| PCI启动I/O写 | 32长字 |

| PCI目标读 | 16长字 |

| PCI目标写 | 32长字 |

| DMA读 | 32长字 |

| DMA写 | 32长字 |

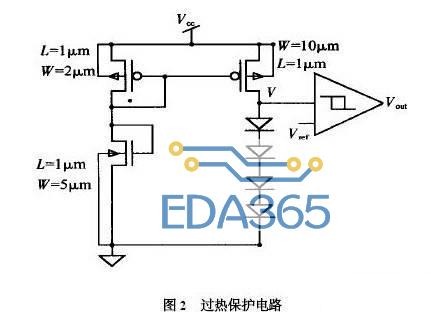

利用PCI 9054芯片构成的PCI适配器典型框图如图2所示。

2 PCI 9054外接FIFO的设计

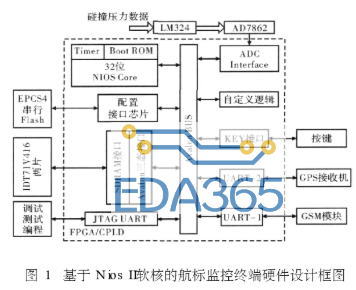

PCI 9054内部有6种FIFO用于提高数据传输速率,解决本地总线和PCI总线之间的异步接收。但挂于PCI 9054本地总线的速率往往较慢,为了保证可靠性,往往需要扩充FIFO加以缓存。下面以IDT 72205FIFO为例,介绍用PCI 9054本地总线扩充FIFO的具体设计方法。

2.1 9054工作方式选择

PCI 9054可工作在M,C,J三种模式,其中C模式时序较为简单。本设计选择PCI 9054工作在C模式,总线周期采用“PCI目标读单周期”以及“PCI目标写单周期”。下面介绍部分引脚信号。

LHOLD:输入信号,申请使用本地总线。

LHOLFA:输入信号,对LHOLD应答。

ADS:输出信号,表示新的总线访问有效地址的开始。在总线访问的第一个时间周期设置。

BLAST:输出信号,表示总线访问的最后传送。

LW/R:输出信号,高电平表示读操作,低电平表示写操作。

LA:地址线。

LD:数据线。

READY:输出信号,表示总线上读数据有效或写数据完成。用以连接PCI 9054等待状态产生器,输入信号。

2.2 电路设计

IDT72205是容量为256×18bit的高速、低功耗同步/异步FIFO存储器,具有独立的收、发时钟控制,将之挂于PCI 9054的本地总线可以实现PCI 9054 FIFO的扩充。图3为PCI 9054和IDT 72205连接的电路图。

对CPLD要求:当EF=1(FIFO不空),LW/R=0,LCLK为上升沿时,OE产生负脉冲,宽度为2时周期。

PCI 9054是一种功能/价格比高的PCI桥路芯片,比PCI 9080,PCI 9050等性能更优越。本文设计的FIFO扩充方法具有通用性,可用于PCI 9054本地总线其它I/O或存储器的扩充。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多