引言

功放进入了数字时代。数字功放的关键部分集成电路已经达到了较高水半,如TDA8902J数字功放有效地降低了信号间的干扰、可实现高保真。虽然核心技术解决了,但印制线路板(PCB)布线不当,也很难达到理想的效果。笔者在TDA8902J数字功放的PCB设计过程中总结了一点经验,现就PCB设计应遵守的布线原则及抗干扰设计要求与电磁兼容性要求作简要分析介绍。

1 PCB的布局及布线原则

PCB提供了功放电路元器件之间的电气连接,要使功放电路获得最佳性能,元器件的布局及印制导线的布设是关键。

1.1 布局原则

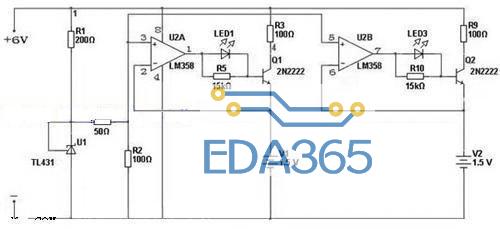

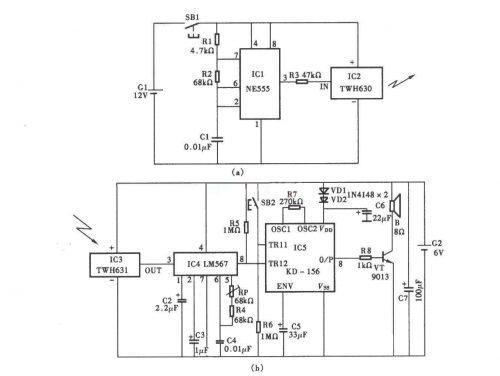

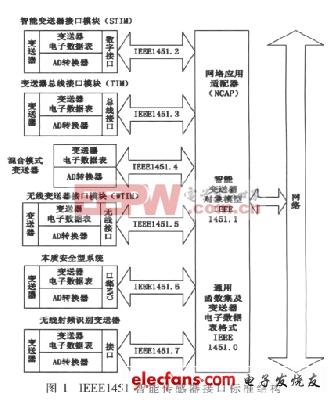

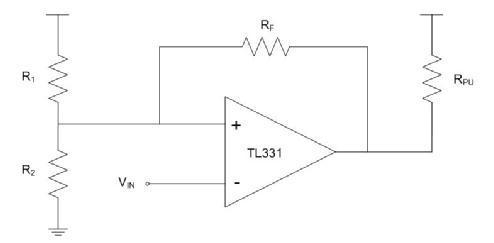

(1)数字功放的功率管工作在开关状态,频率高、电流大,且与电源部分靠得近,而该功放(如图1—1)由于采用开关电源(图中未画出)供电,干扰和纹波系数较大,因此,元器件在PCB上排列的位置要考虑抗电磁干扰,各部件之间的引线要尽量短。在布局上,要把模拟信号、数字信号和噪声源这三部分合理地分开,使相互间的耦合为最小。即要求与LM4651⑩脚相连的模拟输入部分与其它数字部分要分开,电源输入、去耦滤波元件,也要与数字处理部分分开,此外,还要考虑电源变压器的方向性,使之对电路的辐射最小。

(2)元件在排列时应按输出滤波器、H-桥电路、比较器、振荡发生器、电压放大器的次序,如果各级交叉排列,很容易相互影响,出现自激或吸收。

(3)对电磁场辐射较强的元件(如L3,L2)、和对电磁感应较敏感的元件(R1、C1,R5、C3),应加以屏蔽,或远离电磁场辐射源,以减少干扰。

(4)尽可能缩短高频元件(如R5、C3)之间的连线,设法减少它们的分布参数和相互间的电磁干扰。易受干扰的元器件不能相互挨得太近,输入和输出元件应尽量远离。

(5)有些元器件或导线之间有较高的电位差,应加大它们之间的距离,以免放电出现意外短路。如TDA8902J的⑤、⑦脚:LH4652的①、③脚走线不宜相距太近。带高电压的元器件(如电源开关)应尽量布置在调试时手不易触及的地方。

1.2 布线原则

(1)输入输出端(如R8、L1)用的导线应尽量避免相邻平行,最好加线间地线,以免发生反馈耦合。

(2)各级走线应尽可能短,元件应尽量靠拢,大信号、高阻抗走线更要注意。如R11、C18的走线应尽可能短,音频的输入(C1 、R1)输出(L1、L2)线也不宜长,否则易感应交流信号。

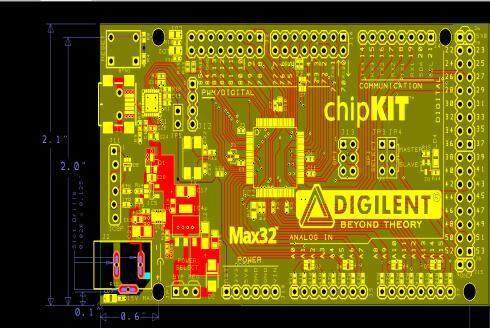

(3)导线的最小宽度主要由导线与绝缘基板间的粘附强度和流过它们的电流值决定。当铜箔厚度为0.05mm、宽度为1—15mm时,通过2A的电流,温度不会高于3℃。该功放可选0.5~5mm导线宽度。导线的最小间距主要由最

APP下载

APP下载 登录

登录

热门文章

热门文章