0 引言

随着电路设计的多样化,电路测试也对信号源提出了更高的要求。传统的信号源只能产生几种固定的波形,灵活度较差。任意信号发生器(AWG)很好地满足了这个要求,它不仅可以输出标准信号,而且可以方便地产生任意波形,在测控、通信,医疗等领域有着广泛的应用。任意信号发生器通常采用直接数字频率合成(direct digital frequency synthesizer,DDS)技术实现。DDS技术是J.Tiemev在1971年首次提出的一种以全数字技术,它从相位概念出发直接合成所需波形的一种新的合成原理。Qt是一个跨平台的C++图形用户界面应用程序框架。它提供给应用程序开发者建立图形用户界面所需的所用功能。Qt是完全面向对象的,模块化程度非常高,很容易扩展,并且允许真正地组件编程。 Qt具有优良的跨平台特性,支持多种系统和平台,包括Windows系统,所有的UNIX系统以及嵌入式系统等。Qt遵循GPL(general public lice-nse)协议,开放主要的源代码,用户可以在GPL的规定下自由添加新特性。

1 DDS模块的设计

1.1 DDS在FPGA中的实现

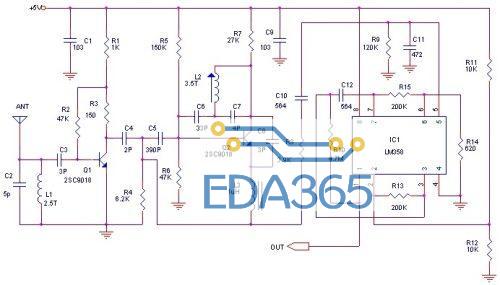

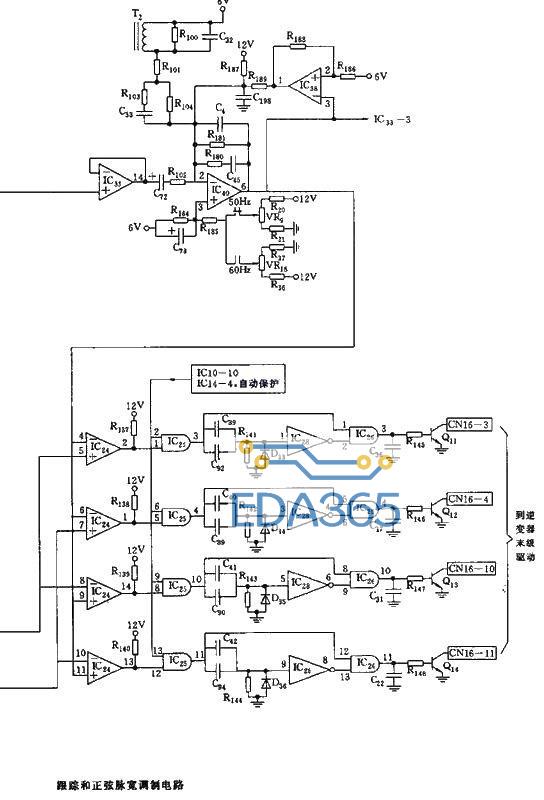

DDS由相位累加器,波形存储器,D/A转换器,低通滤波器等部分组成。该系统的DDS模块根据需要做了适当的修改。其结构框图如图1所示。

(1)增加了通信接口电路和DD8控制模块用于接收用户数据和控制DDS的运行状态。

(2)基准时钟采用5 MHz,经过可控分频器分频后作为DDS的时钟信号,周期分辨率最高可达200 ns(即分频为1)。

(3)相位累加器的频率控制字固定为1,相位控制字固定为0。

(4)波形存储器采用RAM,可以写入用户自定义的波形数据以产生任意波形,其地址宽度设置为11 b,这样存储深度可达2K点。

(5)电平偏移电路用于消除D/A输出信号中叠加的无效直流分量,对于有效的直流分量会保留。

1.2 通信接口及控制寄存器的设计

DDS控制寄存器控制整个DDS模块的运行参数和状态,并通过通信接口接收来自ARM的数据。根据需要共设置了8个寄存器,地址从O~7。其功能和分配如表1所示。

表1其中:

(1)0~3 B存储分频参数,占用32位,因此分频范围为1~232。

(2)4~5 B存储相位累加器的参数,用于控制波形点数和触发模式,其各位的含义如表2所示。

APP下载

APP下载 登录

登录

热门文章

热门文章