引言:

模拟

电压缓冲器是混合信号设计中非常重要的基本组成部件。它们主要用作信号监听和驱动负载。在第一种情况下,缓冲器通常连接到测试电路和要求低输入电容的电路的内部节点,因为这个节点上寄生电容的任何增加可能都是至关重要的。然而,当缓冲器用来驱动负载时,为了在整个电源电压范围内尽快地驱动负载,我们希望大范围输出信号摆幅内具有高的转换速率。

目前集成电路的电源电压已经降低了,主要集中在功耗和可靠性问题。这种趋势已经迫使大部分模拟

基本组成部件重新设计,试图保证它们的整体性能。在这些设计约束下。轨到轨操作在低压设计中成为强制性的,目的是为了增大信噪比。

在这篇文章里,我介绍了一种能达到AB类特性轨到轨CMOS模拟

缓冲器的电路技巧,产生了具有低功耗和高的驱动能力的方法。

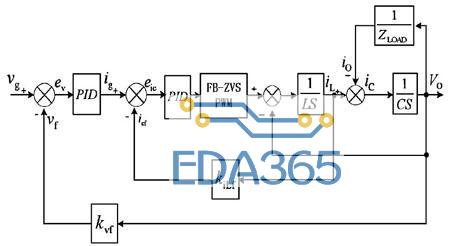

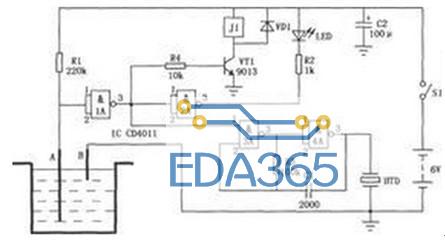

以前的互补:图1a给出了P沟道AB类差分对,当大的差分信号加到输入端时,它能够传送非常大的电流。在差分对节点A处的阻抗非常低,而且它的电压即使在的输入信号下,也近似接近常数。因此,差分电压V1-V2在M2上产生大的电流变化,在M3上也同样如此。

AB类电压缓冲器可以通过连结两个互补差分单元而得到,如图1c所示。毫无疑问,图1c中的电路有两种局限性。第一,M3P和M3N的栅源电压可以分别迫使驱动晶体管M1P和MlN在三极管区工作,减小了可用的电压工作范围。这种缺陷可以通过引进电压电平移位器来驱动M3P和M3N来克服,这将在后面解释。第二,当输出节点接近正向或者负向电源轨时,这种结构的输出电压摆幅受到限制。主要是因为P沟道和N沟道差分对分别工作在VDD和VSS受到限制的缘故。

图1 AB类差分输入单元;对差分信号的直流传输特;基于两对互补AB类差分输入单元的低功耗缓冲器

a AB类差分输入单元 b DC传输特性 c低功耗缓冲器

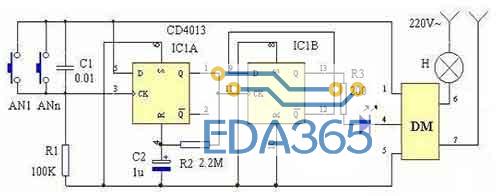

所提出的模拟

缓冲器:图2给出了晶体管级实现所提出的轨到轨MOS模拟

缓冲器。这种电路是单增益级。它的输人支路是由两个互补的AB类差分对组成。与图1c中电路的重要区别是,在这种情况下,输出节点不是由输入驱动直接驱动,而是由电流镜M4P-M5P和M4N-M5N分别驱动。因此,M2P和M2N的共栅现在是不倒相输入端。

图2所提出的轨到轨AB类缓冲器

在中部电源电压区,PMOS和NMOS输入对是有效的,而且它们的偏置电流通过电流镜M4P--M5P和M4N--M5N镜像到该电路的输出端。这种结构允许NMOS输入对驱动在电源电压区的输出节点接近VDD.而PMOS控制输出端的电压范围接近VSS.不幸的是,在接近VDD时,P沟道输入对截止,而且没有电流被镜像到输出端的底部,关闭了缓冲器。类似的情况是VSS时.N沟道差分对不是有效的。为了这个原因,晶体管M1PR-M5PR和MlNR-M5NR已包括在图2中,维持在整个电压范围内是有效的。

因此,这种缓冲器的工作过程可以这样详细描述如下:当输入信号Vin,在中部电源电压区,两个输入对MIP~M2P和MlN―M2N是有效的,M4P-M5P和M4N--M5N镜像一个等于IB的电流到输出支路。而且,电流IB的复制品通过晶体管MIPR(M1NR)和M2PR―M3PR(MlNR―M2NR)拷贝,给输出支路底部的附加电路的电流源提供电流。因此,晶体管M4P和M5P(M4N和M5N)关断,而且对输出电流没有任何贡献。输入信号接近VDD时,PMOS输入对关断,而且反相输入支路的复制品等等都关断。MIPR--M3PR不对输出支路的附加电路发送任何电流。这样的话,M4PR和M5PR导通,从输出支路吸收等于IB的电流,维持缓冲器是导通的。当输入信号Vin接近VSS时,类似的情况也会发生。

APP下载

APP下载 登录

登录

热门文章

热门文章