引 言

偏振控制器是一种重要的光器件,在光纤通信和传感领域都有着广泛的应用。实际运用中,偏振控制器的半波电压与厂家给出的标称值并不完全一致,导致了使用的不便。因此在使用时需要有与之配套的驱动电路。但是,许多厂家并不提供配套的驱动电路,即使提供,价格也昂贵,在实际工程开发中不能达到最佳性价比。因此,自主研制DPC的驱动电路是很有必要的。

本文以光纤挤压型偏振控制器为研究对象,运用邦加球图示法分析了其工作原理,并介绍基于DDS技术和FPGA的动态偏振控制器驱动电路的工作原理、系统结构及软、硬件设计。测试结果表明,设计实现了驱动电路的预定功能,生成了4路频率幅值均可调的正弦驱动信号。

1 DPC的工作原理

这里研究的光纤挤压型偏振控制器,其内部结构如图1所示。它由4个压电陶瓷光纤挤压器(称为挤压器F1,F2,F3,F4)组成,其方位角分别为0°,45°,O°,45°,各挤压器对应的驱动电压为V1,V2,V3,V4。分别在4个挤压器上加电压信号驱动,产生相应的压力挤压光纤,形成线性双折射,改变入射光波的相位差,从而实现任意偏振态转换。

由文献[3—5]和上述偏振控制器内部结构,可将挤压器中的四段光纤(分别称为d1,d2,d3,d4)看成不同方位角的相位延迟器。

(1)d1,d3可看成方位角为零的相位延迟器,只改变输入光的相位延迟而不改变其偏振方向,在邦加球上表现为输入偏振态绕S1轴的旋转。

(2)d2,d4可看成方位角为45°的相位延迟器,也即旋光器和相位角为零的相位延迟器的合成,不仅改变输入光的相位延迟,也改变其偏振方向,其偏振态变换在邦加球上表现为绕S2的旋转。

图2为d1,d2,d3,d4对偏振态变换在邦加球上的显示。如图2所示,在邦加球上,随所加电压的变化,d1或d3的输出光起始偏振态S绕S1轴顺时针旋转。d2,d4的输出光偏振态S'随所加电压变化在邦加球上绕S2轴逆时针旋转。

图2光纤挤压器偏振态随电压变化的邦加球示意图由此可知,只要输入光的偏振态与F1和F2的方向都不垂直,则输入光的偏振态都可以通过操作至少2个挤压器改变到任意一个偏振态。

2 DPC的驱动电路设计

DPC驱动电路的设计基于DDS技术,系统主要由Xilinx Spartan-3系列FPGA、数/模转换器LTC1668及宽带放大器LT1812组成。

2.1 DDS的基本原理

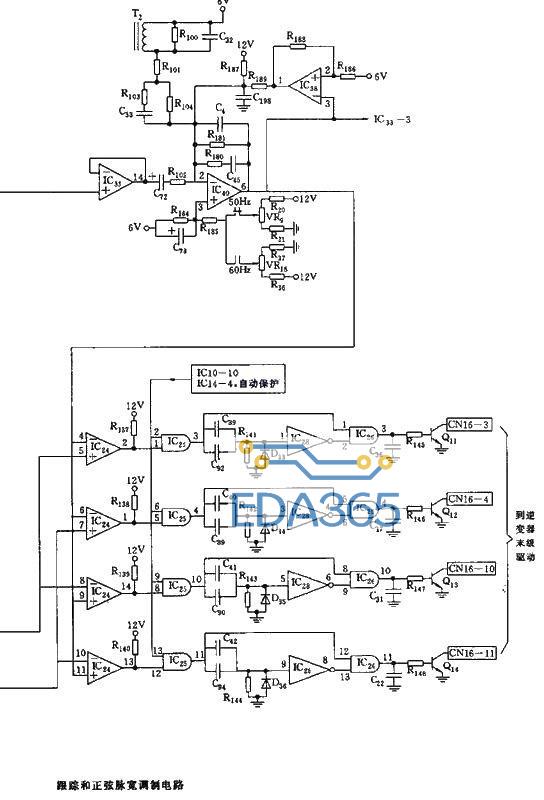

DDS的基本原理是基于采样定理。将相位累加器输出的相位码通过查表法映射成波形幅度码,经模/数转换和低通滤波后产生波形,其框图如图3所示。它主要由参考时钟fref、相位累加器、相位寄存器、波形存储器、数模转换器及低通滤波器等部分构成。

DDS工作时,它将在时钟脉冲的控制下,对频率控制字F用累加器进行处理,以得到相应的相位码;然后由相位码寻址波形存储器进行相位码——幅度编码变换后输出不同的幅度编码;再经过数模转换器和低通滤波器处理,即可得到由频率控制字决定的连续变化的输出波形。

2.2 硬件组成

DPC的驱动电路是基于偏振度测试系统平台(见图4)研制的。DPC用于将输入光扰偏后输出,再经检偏器和探测器将光强信息转化为数字量送入FPGA,FPGA对数据进行处理后再对DPC的驱动电压做出调整并输出,以达到完全扰偏的目的。

要实现完全扰偏,也即是让输入偏振态在一定时间内遍历各个偏振态。根据DPC的工作原理及实验尝试,测试系统使用4路正弦信号同时驱动4个光纤挤压器。根据DPC自身性质,所需提供电压最大值应小于2 V,正弦波频率应小于2 000 Hz。因此,驱动电路需要提供4路大于零的正弦波驱动信号,其峰值应小于2 V。且正弦波频率各不相等,均小于2 000 Hz。

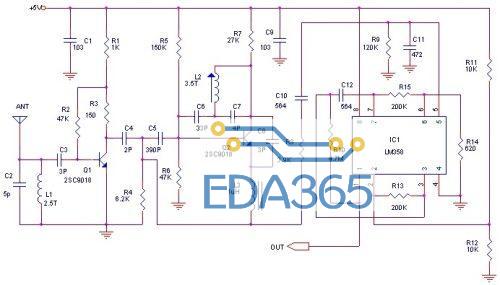

驱动电路的硬件结构如图5所示,4路电压驱动设计均相同。采用16位高精度数/模转换器LTC1668,将FPGA输出的数据转换为模拟电流,再经运放LT1812将电流转换为电压。

APP下载

APP下载 登录

登录

热门文章

热门文章