将宽带DAC互补电流输出转换为单端信号的传统方法是使用中心抽头变压器,或者在差分转单端配置中使用一个单通道运算放大器。然而,变压器的低频非线性可能会限制其在DC 附近使用;运算放大器方法则要求电阻严格匹配,以提供直流共模抑制、负载阻抗和互补DAC输出之间的增益匹配。如果匹配有误差,则最终输出也会产生误差。本电路利用差分接收放大器 AD8130 实现简单的差分转单端功能,无需使用昂贵的精密电阻,从而以更少的元件提供更高的精度。

AD8130 还有一个优势,即具有业界领先的交流共模抑制性能(10 MHz 时为 70 dB)。可以利用这一特性抑制 DAC 数字地层与接收器模拟地层之间的噪声,这是此类混合信号应用的一个常见问题。

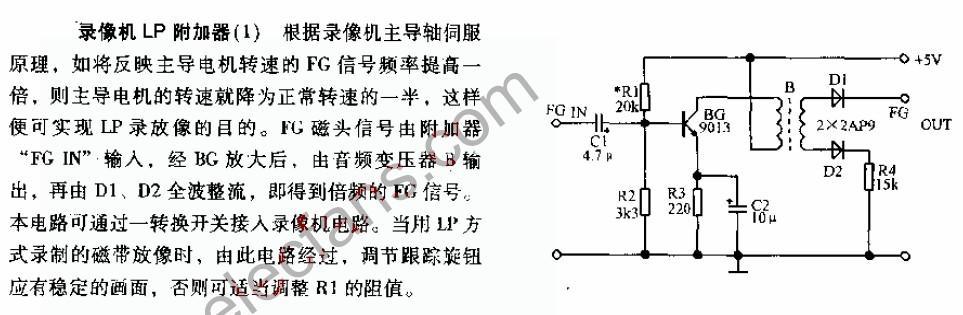

电路描述

本电路采用 20 mA互补电流输出、低功耗、14 位、125 MSPS、双通道TxDAC®数模转换器 AD9117 和低成本、270 MHz差分接收放大器AD8130。

通过改变 FSADJI 或 FSADJQ 与地之间的电阻值,可以在 4 mA 至 20 mA 范围内调整 AD9117 的满量程输出电流。本例使能了内部电阻选项,并将其设置为 1.6 kΩ,以便提供最大20 mA 电流输出。该配置要求将 0b10100000 写入 AD9117 的寄存器 IRSET 和 QRSET。互补电流输出采用 49.9 Ω 外部电阻端接,以产生差分电压。采用满量程数字输入摆幅时,这些电阻上产生的电压彼此相差 180°,大小介于 0 V 至 1 V 之间,因此峰峰值差分输出电压为 2 V。一个 47 pF 电容与这些负载电阻并联,构成一个 68 MHz 一阶重构滤波器,并衰减奈奎斯特带宽之外的镜像。与 AD8130 输入引脚串联的两个49.9 Ω 电阻可改善电路的整体失真性能。共模输出引脚 CMLI 和 CMLQ 可以用来提供附加偏移,但本例中未使用,而是将其接地。

AD8130 是一款理想的互补产品,因为它有较大的平衡输入阻抗,可以将差分输入轻松转换为单端格式,并具有出色的交流共模抑制性能,如下图所示。

AD8130 带宽为 270 MHz,支持 AD9117 在最大更新速率 125 MSPS 时产生的最高达约 40 MHz 的 DAC 输出频率。

本例中,AD8130 的增益设置为 1(RF = 0,省去 RG)。不过, 只需改变 R /R 比,就能调整增益。电源设置为±5 V,但如果输出端需要更大摆幅,可以将其提高至最大±12 V。

为使本电路正常工作,必须考虑与 DAC 和运算放大器相关的裕量问题。DAC 输出电压需保持在其规格范围内,防止内部电路引入失真。当 DAC VDD = 3.3 V 且 VCM = 0 V 时,AD9117 输出必须小于±1 V,这可以通过 49.9 Ω 负载电阻和 20 mA 满量程电流来实现。当放大器输出端负载为 1 kΩ 时,AD8130 要求 1 V 的电源电压裕量;因此,当采用±5 V 电源时,输出摆幅不能超过±4 V。

谐波失真是本设计的重要标准。下图显示了整个电路(AD9117 + AD8130)的二次和三次谐波失真测量结果,以及AD9117 本身的谐波失真。测量在AD8130 的增益设置为 1(RF = 0,省去RG)的条件下进行。

如果时域应用需要更快的上升/下降时间,可以通过减小电容值来提高重构滤波器的截止频率。不过,与 AD9117 DAC 的内在性能相比,AD8130 的 270 MHz 带宽会限制上升/下降时间和建立时间。该电路仍然可以在 3 次 DAC 更新(125 MSPS)的时间内建立。0.1 μF电容对AD9917 内部基准电压源去耦。应将一个 0.1 μF 低电感陶瓷去耦电容与VDD相连,并使其非常靠近AD9117。

将AD8130 的引脚 4 和RG连接到一个失调电压(VOFF),可以独立于放大器增益来调整AD8130 的输出电压失调,使其值不为 0 V。该配置中,VOFF出现在单位增益输出端,而AD8130 的增益仍然为 1+RF/RG。

为了使本文所讨论的电路达到理想的性能,必须采用出色的布线、接地和去耦技术。至少应采用四层 PCB:一层为接地层,一层为电源层,另两层为信号层。

所有IC电源引脚都必须采用 0.01 μF至 0.1 μF低电感多层陶瓷电容(MLCC)去耦至接地层(为简明起见,图中未显示),并应遵循各IC数据手册的相关建议。

APP下载

APP下载 登录

登录

热门文章

热门文章