时钟同步问题讲完了,下面就开始讲讲soc中另一种常见的情况,有时为了考虑到功耗,性能的问题,某个模块可能在某一种情况下工作在一个频率,另一种情况下工作在另一种频率,这个时候就需要进行mux的切换,有的人就会说了,哪简单啊,加个mux啊,可事实真的如此吗?

时钟同步问题讲完了,下面就开始讲讲soc中另一种常见的情况,有时为了考虑到功耗,性能的问题,某个模块可能在某一种情况下工作在一个频率,另一种情况下工作在另一种频率,这个时候就需要进行mux的切换,有的人就会说了,哪简单啊,加个mux啊,可事实真的如此吗?

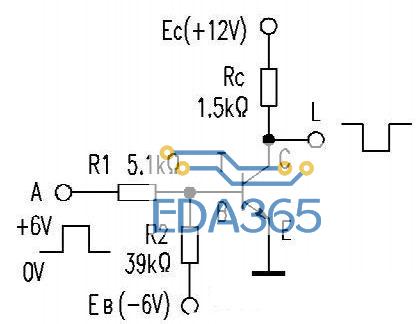

那么该如何消除毛刺,进而消除后面可能带来的问题呢,见下图,加入反馈电路。

反馈是为了确保时钟真正被关闭了,例如,select从0切换到1,也就是选择clk1,但是这时要确保clk0被完全关闭了,所以通过clk0时钟域的DFF反馈回来的1(如果能反馈1说明0已经进入到clk0时钟域的DFF中了)与clk1时钟域的select进行相与。

另外,为了解决跨时钟域的问题(select毕竟是不同于clk0,clk1时钟域的),通常还会加入1-2级的DFF。

另外,这几个电路使用时需要注意一点的是两个clk都必须要震荡起来后才可以进行select,否则进行切换可能导致select不能被正确的传送到最后一级的与门上,这样消除毛刺的功能可能就无效。

APP下载

APP下载 登录

登录

热门文章

热门文章