本文根据一个实用的电路设计阐述了如何设置高速ADC MAX1196的共模输入范围。

输入共模电压范围(Vcm)对于包含了基带采样和高速ADC的通信接收机设计非常重要,尤其是采用直流耦合输入、单电源供电的低压电路。对于单电源供电电路,馈送到放大器和ADC的输入信号应该偏置在Vcm范围以内的直流电平,能够消除放大器和ADC设计的一大屏障,因为不必在0V保持低失真和高线性度。

直接下变频结构的无线通信接收机通常采用差分、直流耦合方式与ADC连接。这种电路包含一个零中频(ZIF)结构,具有一个RF正交解调器和双通道基带ADC。ZIF电路省去了多级IF下变频器和SAW滤波器,因而受到了普遍欢迎。

ZIF结构采用直流耦合方式主要基于以下原因:它们接收的同相(I)和正交(Q)基带数据的带宽扩展到了直流附近;另外,这种架构消除了RF下变频器与高速ADC之间的大电容,同时也消除了耦合电容放电引起的上电延迟。

从下列内容可明显看出Vcm对于ADC的重要性:

电源电压(VDD)变化时, RF正交解调器提供给ADC的信号具有很宽的共模电压范围。

超出ADC Vcm范围的输入共模电压会产生谐波失真,从而降低动态范围。适当的Vcm直流偏置有助于优化放大器和ADC的线性指标、减小失真、降低误码率(BER)。

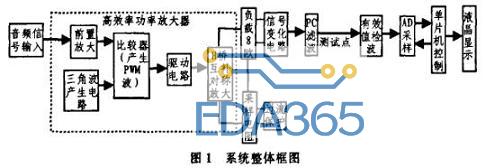

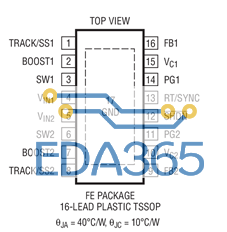

图1所示电路中,U1简化了射频前端、放大器和ADC之间的直流耦合以及差分模拟接口。电路中使用了一片双路、8位、40Msps ADC (U1)和两片单电源供电的宽带、四运放(U2-U3),为RF正交调制器(差分、直流耦合信号源)与高速ADC之间的模拟接口提供宽范围的输入共模电压。ADC具有足够高的信号与噪声+失真比(SINAD)和无杂散动态范围(SFDR),用于3.84MHz宽带QPSK通信链路的检波。须合理选择U2和U3,以满足SFDR和输入共模范围的要求。单电源3V供电时,U1的功耗是90mW。

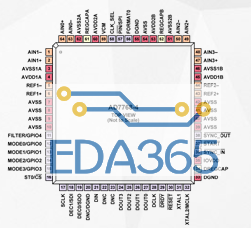

图1. 高速ADC (U1)利用其COM输出精确设置共模电压。

U1的直流共模输出(COM,引脚1)、REFIN (引脚46)和REFOUT (引脚45)简化了Vcm的转换。COM提供VDD/2直流输出,无论VDD怎样变化,都能够满足U1输入共模范围的要求。REFIN和REFOUT通过分压电阻R23-R24设置ADC的满量程范围,优化输入放大器的SFDR和ADC动态范围。

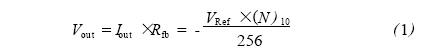

U2和U3配置成直流耦合、差分输入/输出,具有14dB增益,给ADC提供1VP-P的满量程输入(FS)。为保证接收机的动态范围要求,U2/U3放大器的SFDR需要比ADC的48.7dB SINAD提高10dB。U1的满量程电压由R23和R24设置:

FS = R24 / (R23 + R24) x REFOUT (其中, = 2.048V)

COM电压(U1的引脚1)等于VDD/2,或1.5V (VDD = 3V)。这个电压也等于U1的共模输入范围Vcm。当VDD随温度和电源电压变化时,COM电压和Vcm彼此保持一致。COM引脚可以供出5mA电流,可以根据需要设置系统其它电路的直流电平。当ADC关断时,内部COM缓冲器也关断,所以用它设置电平比连续工作的电阻分压器更省电。

图1电路的典型应用是WCDMA接收机,每路ADC输入是3.84Mcps码率的一半。当U1以四倍的码片速率进行过采样时(Fclk = 15.36MHz),可以提供两个好处:首先,过采样简化了抗混叠滤波器的设计,镜频达到13.44MHz和17.28MHz (FI = Fs ± Fa),超出两倍频程;其次,过采样可以获得6dB的处理增益:SNR=10log (Fs/2BW)。

UI的数字输出由OVDD = +1.8V决定,有助于降低功耗。+1.8V总线减小了数字信号摆幅,因而降低了功耗:P = CV2F (8位总线的每一条),UI的数字输出是复用的,允许一组8位总线连接两路8位ADC。复用总线可以减少引脚数,节省电路板面积,降低数字ASIC的成本,并提高系统的可靠性。

可以选择其它芯片:MAX1185双路、10位ADC,与MAX1196引脚兼容,均采用带裸焊盘的7mm x 7mm、48引脚TQFP封装。MAX1192是超低功耗、更小封装的双路、8位ADC,功耗为25mW/3V,采用5mm x 5mm、28引脚薄型QFN封装。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多