引言

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,可测性设计(DFT)的功耗问题引起了VLSI设计者越来越多的关注。因为在测试模式下电路的功耗要远远高于正常模式,必将带来如电池寿命、芯片封装、可靠性等一系列问题。随着集成电路的发展,内建自测试(BIST)因为具备了诸多优越性能(如降低测试对自动测试设备在性能和成本上的要求、可以进行At—speed测试及有助于保IP核的知识产权等),已成为解决SoC测试问题的首选可测性设计手段。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。

另外,在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而由LFSR产生的连续测试模式之间的相关性很低。因此,在自测试期间会增加电路中节点的翻转活动,导致功耗增大。

2 功耗分析和WSA模型

CMOS电路中功耗的来源主要分为静态功耗和动态功耗两种。漏电流或从电源供给中持续流出的其它电流导致静态功耗。动态功耗则是因为短路电流和负载电容的充放电,从而由电路正常工作时的功能跳变所引起的,它包括功能跳变、短路电流、竞争冒险等。对于CMOS工艺来说,目前动态功耗是电路功耗的主要来源。

对于节点i上每次开关上的功耗为:

式中,Si是单周期内翻转的次数,Fi是节点i的扇出,C0是最小输出负载电容,VDD是电源电压。

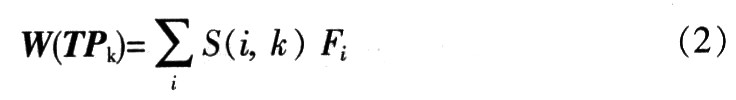

从式(1)看出,门级的功耗估计与Si和Fi的乘积和节点i的翻转次数有关。节点的扇出由电路拓扑决定,而它的翻转次数由逻辑模拟器来估计。这个乘积即称为节点i的权重翻转活动(Weighted Switching Activity,WSA)。在测试过程中WSA是节点i功耗Ei的唯一变量,所以WSA可作为该节点的功耗估计。对于一对连续的输入矢量TPk=(Vk-1,Vk),电路总的WSA为:

式中i是电路中所有节点的个数,S(i,k)是由TPk所激励节点i的翻转次数。

根据式(2),考虑长度为L的测试矢量TS作为电路的输入矢量,电路总的WSA为:

根据以上功率和能量消耗的表达式,再给定一个电路设计为CMOS的工艺和供给电源,可得以下结论:

(1)电路中节点i的跳变数成为唯一的影响能量、最大功耗和平均功耗的参数。

(2)测试中时钟的频率也影响着平均功耗和最大功耗。

(3)测试长度,即施加在待测电路(CUT)上的测试向量的数目一只影响总的能量的消耗。

3 LFSR优化的低功耗方法

通过对测试过程的功耗分析可知,选择BIST低功耗的方案时,一方面可以通过减少测试序列长度来实现(但该方法往往以牺牲故障覆盖率为代价),另一方面降低WSA值也可实现系统功耗的降低。

在BIST结构中,线性反馈移位寄存器(LFSR)由于结构的简单性、规则性、非常好的随机测试矢量生成特性、用来压缩测试响应时的混淆概率非常小等特点,在DFT的扫描环境中很容易集成,所以当从扫描DFT设计升级成BIST设计时,LFSR因其硬件开销很小而成为BIST中应用最广的矢量生成结构。

基于LFSR优化的BIST结构可分为test—per-一scan和test—per—clock两类结构。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展:而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。

3.1 基于扫描的test—per—scan方式

3.1.1 基本结构

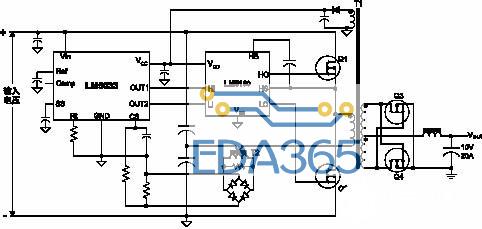

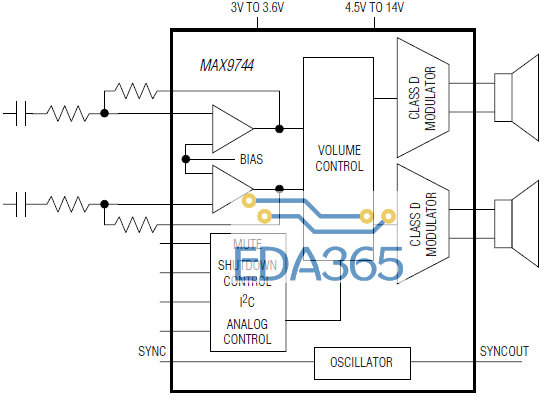

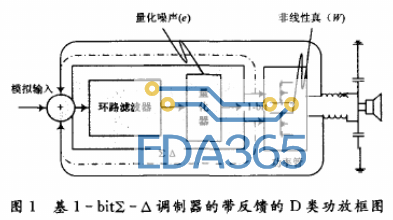

test—per一scan内建自测试的目标是尽可能的降低硬件开销。这种结构在每个输入输出端口处使用LFSR与寄存器的组合来代替LFSR。图l是test—per-scan内建自测试的基本电路结构。在内建自测试矢量下,LFSR生成测试矢量并且通过扫描移位寄存器(shift register)将测试矢量移位到待测电路(CUT)的输入端,同时响应被移入LFSR并压缩。

3.1.2 原理

全扫描或部分扫描设计中由于移位会产生比较大的功耗。基于扫描的test一per-scan低功耗设计方法需要修改标准的扫描设计,降低状态转换活动率。没计修改包括在移位期间用于屏蔽扫描路径活动的一些门控逻辑,以及对用于抑制随机模式的附加逻辑进行综合等。

3.1. 3 部分扫描算法

根据以上扫描设计原理,在消除测试序列中的冗余模式之后,采用图2所示的部分扫描算法对待测电路进行部分扫描设计。其步骤如下:

①首先删除所有自反馈时序逻辑对应的顶点。

②在数据流图中查找所有的强连通单元(Strongly Connected Components,简称SCC)。

③依次删除SCC所有顶点中最大的顶点。

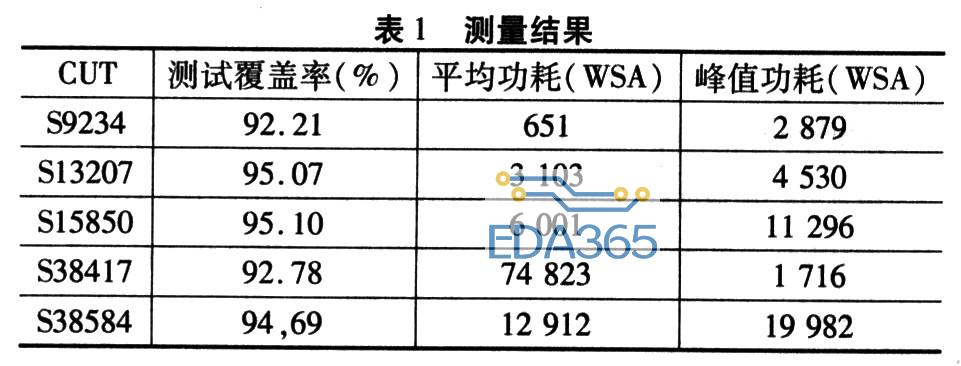

参考文献采用上述算法对ISCA89基准电路扫描BIST测试,并采用ATPG工具和仿真工具VCS故障模拟和功能模拟,表1列出测试覆盖率、平均功耗和峰值功耗数据。

由表l数据可见,部分扫描对待测电路测试覆盖率影响非常小(《3.5%),且对电路进行部分扫描设计后,扫描寄存器数目大大减少,所以在扫描移位周期需要同时触发寄存器的数目也大大减少,由此引起待测电路内部节点的翻转数目也大大减少,可达到降低BIST的平均功耗和峰值功耗的目的。

3.2 基于时钟的test—per-clock方式

3.2.1 基本结构

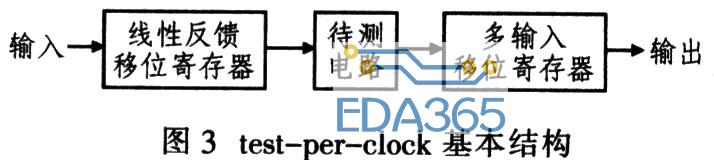

一个test-per-clock内建自测试基本结构如图3所示。每一个测试时钟L2SR生成一个测试矢量。多输人特征寄存器(MulTIple-一Input Signature Register,简称MISR)压缩一个响应矢量。

3.2.2 原理

在扫描测试中,主要功耗包括逻辑功耗、扫描功耗和时钟功耗。前面给出的方法主要集中在降低逻辑功耗或扫描功耗,但没有降低时钟功耗。基于时钟的低功耗test—per—clock方式可以同时降低这3种功耗。该方法采用低功耗的test—per-一clock BIST结构。对LFSR进行修改后,用作TPG以生成低功耗的测试矢量。使用这种经过修改的时钟方案会降低被测电路、TPG和馈给TPG的时钟树的跳变密度。通过降低被测电路、TPG和时钟树的状态转换活动率来降低BIST期间的功耗。

由于来源于标准扫描结构的测试模式可直接用于低功耗扫描结构,这种方法与采用传统扫描结构所达到的故障覆盖率和IC测试时间基本一致。与传统扫描结构相比,面积开销很小,在电路性能方面也没有损失。

3.2.3 低功耗测试矢量生成

对于test—per—clock结构来说,减少测试功耗主要通过优化测试矢量来实现,而测试矢量生成技术是指产生确定性测试矢量的技术。

测试矢量生成方式在生成测试模式时,除了要达到传统的ATPG目的,还需考虑降低测试期间的功耗。基于ATPG的方法又分为2种:①集成的ATPG优化方法,该方法的测试模式在测试生成期间进行低功耗优化;②ATPG之后的优化方法,该方法的测试模式首先由传统的ATPG生成,然后再进行功耗优化。

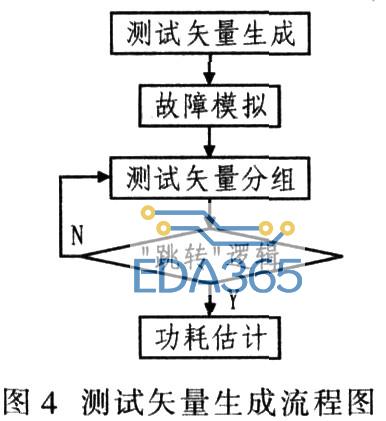

(1)与模拟退火算法相结合测试矢量生成的步骤是:首先根据模拟退火算法将测试模式分组成若干个有效测试矢量组与无效测试矢量组两部分;然后根据算法原理,生成控制LFSR运行的控制码;在这些控制码的作用下,LFSR就跳过大量的无效测试矢量,生成由有效测试矢量构成的精简的测试矢量序列。其基本流程如图4所示。

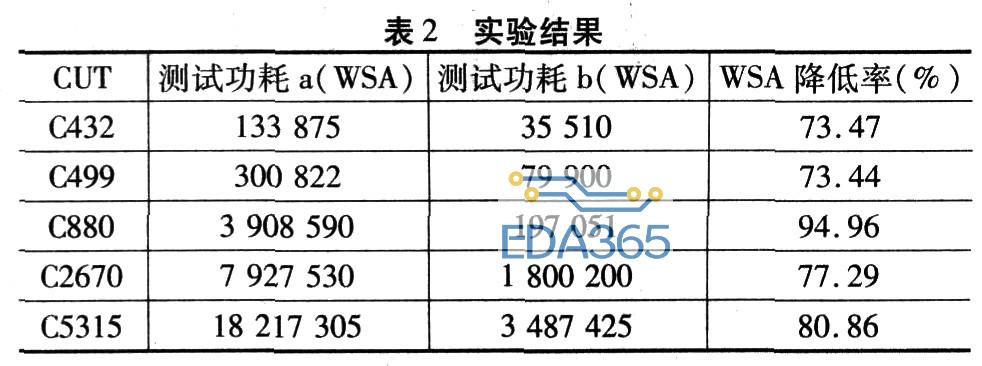

(2)与进化算法相结合依据测试矢量生成技术原理,采用基于遗传算法的测试模式生成器,用于计算冗余的测试模式。在冗余测试模式中,一个故障由几个不同的序列覆盖。然后使用一个优化算法,从前面已计算过的测试序列组合中选择一个最佳子集,使其峰值功率最小,而不影响故障覆盖率。参考文献采用ISCAS’85Bench—mark中的组合电路作为实验电路,在保持故障覆盖率不变的情况下,对待测电路的测试功耗a与使用模拟退火算法的BIST结构的测试功耗b相比较,得到的结果如表2所示。

由表2可知,满足相同故障覆盖率时,采用模拟退火算法分组测试矢量后,WSA大幅降低,总的WSA改善率在73.44%~94.96%之间。由于减少测试矢量,测试时间也大为缩短。

4 结语

采用线性反馈移位寄存器生成测试矢量的BIST结构可分为test—per—scan和test—per—clock两大类,相应的实现低功耗BIST测试方法也分别针对test一per—scan和test—per一clock结构。对tesl—per-scan结构模式,减少测试功耗主要通过优化扫描链来实现;对于test—per-clock结构模式,减少测试功耗主要通过优化测试矢量来实现。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展;而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。当然,随着测试功耗研究的深入,将会有更好的方法使功耗、故障覆盖率、系统性能等问题达到最优。

责任编辑:gt

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多