摘要:介绍了一个10位100 MHz,1.8 V的流水线结构模/数转换器(ADC),该ADC运用相邻级运算放大器共享技术和逐级电容缩减技术,可以大大减小芯片的功耗和面积。电路采用级联1个高性能前置采样保持单元和4个运放共享的1.5位/级MDAC,并采用栅压自举开关和动态比较器来缩减功耗。结果显示,在输入频率达到奈奎斯特频率范围内,整个ADC的有效位数始终高于9位。电路使用TSMC O.18 μm 1P6M CMOS工艺,在100 MHz的采样频率下,功耗仅为45 mW。

关键词:流模/数转换器;运放共享;栅压自举开关;动态比较器

O 引言

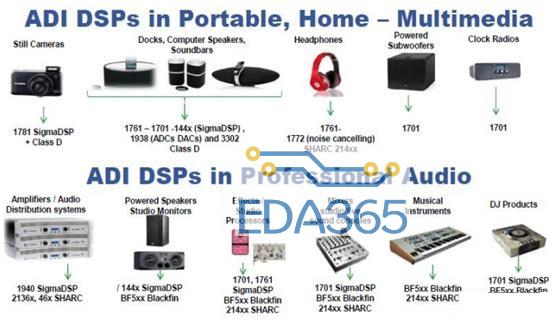

在混合信号集成电路系统中,模/数转换器(ADC)是一个关键的模块。许多现代应用,如数字便携设备、视频处理及无线通信等,都要求具有高采样率、低功耗的模/数转换器。同时,由于许多模/数转换器被使用在电池供电的便携式设备中,降低其功耗就变得越加重要。对于10 b,1 MSPS以上的ADC系统而言,流水线结构是一种合适的设计方案。在此阐述了能够满足10位精度、100 MHz采样率的流水线结构ADC,并且运用了相邻两级共用一个运放的运放共享技术和逐级电容缩减技术来减小功耗和面积。该模/数转换器中采用了低功耗增益提高运算放大器和动态比较器等元件,也更好的降低了功耗。

1 ADC电路结构

1.5位/级结构的ADC具有许多优点,首先每级多产生一位冗余位来进行数字冗余修正,大大减小比较器失调造成的影响。其次较小的单级分辨率可以获得较高的速度。1.5位/级结构的单级闭环增益为2,开关电容电路可以具有较小的负载电容和反馈因子,因此每级可以获得较大的带宽。所以本电路采用1.5位/级级联的结构。

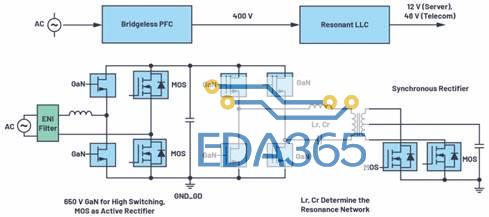

图1为本文所采用的流水线ADC结构,采用了每级1.5位流水线级级联。最前端是一个高性能采样保持电路,虽然采样保持电路需要消耗大量的功耗,但它能够较好地减小由于MDAC和子ADC之间的采样信号失配造成的孔径误差,可以使得电路性能得到较大提高。依次级联8个相同的1.5位/级结构MDAC,最后一级是一个2位的FLASH ADC。所得到的18位数字输出依次经过时间对齐电路和数字校正电路,经过数字校正后得到所需要的10位数字输出。

如图1所示,电路采用相邻级运算放大器共享技术,后面的8个MDAC仅需要4个运算放大器。为了更好地降低功耗,电路使用了逐级电容缩减技术。电路中的Stage 1&2和Stage 3&4采用了相同的运算放大器,Stage 5&6和Stage 7&8进行了缩减,缩减因子为0.7。

1.1 采样保持电路结构

图2为电容翻转型采样保持电路的结构图。相对于电荷转移型的采保电路,这种结构具有较大地反馈系数和较少的电容,使得电路具有实现面积小,噪声低,功耗低,保持相建立时间短等优点,因而更适合于高速的流水线ADC。

该电路工作在采样和保持2个阶段:采样阶段,clkl,clkl_p,clkl_pp为高电平,clk2为低电平,此时输入信号存储在电容上,clkl_PP先于clkl_p和clkl截止,clkl_p先于clkl,采用2个提前截至的时钟波形是为了减小图中采样开关的沟道电荷注入的影响。保持阶段,clkl,clkl_p,clkl_PP为低电平,clk2为高电平,存储于采样电容的电荷传输至采样保持电路的输出并驱动下级负载。该电路的闭环增益为1。

由于开关的开关电阻和电荷注入会对电路产生巨大的影响,图2中的输入采样开关采用了栅压自举开关,这样可以较大的避免与输入信号相关的电荷的注入。

但是,运放共用技术存在2个缺点:一是该技术需引入新的开关,进而引入了串联电阻,该串联电阻与运算放大器的输入电容结合,影响了增益级的建立时间。在高采样频率情况下,通常通过增大开关的宽长比来减小串联电阻,但是增加了开关引入的非线形和失调即沟道电荷注入、时钟馈通。二是运算放大器的输入失调没有时间置零。因此由于放大器的有限增益,每次输入采样值均受前次采样的影响,同时放大器总是工作在保持状态下,其引入的失调电压和1/f噪声亦不能消除。从而影响电路的性能。

在本设计中,为了避免由于运放没有失调消除的过程而产生误差累积的问题,通过增加一个失调消除开关和增加一个失调消除脉冲,可以较好地解决这个问题。

如图3中所示,clkA时钟为运放输入失调消除时钟相,clkl与clk2为整个ADC电路所用的两相不交叠时钟。由于在运放共享结构中,运放在clkl与clk2两相均处于保持状态的负反馈中。为了不改变电路结构和时钟相,在clkl与clk2均为低的时候,引入一个新的时钟脉冲clkA,来开启运放输入端连接到地的一个开关进行失调消除。通过这样在两相不交叠时钟间隙增加一个失调消除脉冲,较好的解决了运放共享结构中输入失调累积所造成的影响。

2 电路设计实现

2.1运 算放大器的设计

为了达到10位以上的线性度,放大器的开环放大倍数至少大于60 dB;为了满足100 MHz的采样频率,放大器的稳定时间需小于5 ns。鉴于上述要求,本文设计的运放为折叠式全差分共源共栅结构,并采用增益增强技术(gain-boost)来提高增益。尽管折叠式共源共栅运放与套筒式共源共栅运放相比较具有功耗大、折叠点处寄生电容较大等缺点,但它却具有高摆幅的优点,尤其是它的输出范围不会受到共模输入电压的影响。这对模/数转换器的动态范围的提高是非常有帮助的。

本文通过调整电路参数,以得到优化的电流,使其恰好同时满足转换速率和建立时间对放大器电流的要求。传统的设计方法只是经验性的使转换速率约为1/2个采样周期的1/3~1/4,因此,它比传统设计方法具有更小的功耗。

运放电路如图4所示,运放的增益为:

图4中Ap,An分别为增益增强的辅助运放,辅助运放同样采用折叠式共源共栅结构。可见增益增强技术引入了辅助放大器无疑极大的提高了主放大器的增益,但是它也在放大器的传输函数中引入了一对零极点对(pole-zero doublet)。尽管它对放大器的频率响应没有影响,但却影响了放大器时域响应。一般要求辅助放大器的单位增益带宽至少与主放大器的带宽相等或稍大,此外要求它的次主极点尽可能大,也就是它的相位裕度要求75°以上。

由于全差分结构需要共模反馈电路来稳定输出的共模电平。常见的开关电容共模反馈电路在两个相位时引入不同的电容负载,这会增加电路的失真和谐波。而连续型共模反馈电路虽然能够在双相时都正常工作,但同时会增加开关电容电路的功耗和影响运放输出摆幅。

本文采用图4中的双相开关电容共模反馈电路,这样的电路适合本电路采用运放共享技术以后,运放需要双相工作的特点。

该共模反馈电路通过增加2个电容和三组开关,使得共模反馈电路能双相工作。其中C1,C2的取值对共模反馈相当重要,较大的C2可以使共模电压更加精确,而C1和C2的比值又决定了共模反馈建立的时间。

运算放大器的几个性能参数见表1。

2.2 改进的栅压自举采样开关

采样开关对整个电路的性能有着至关重要的作用,较大的开关会使得电荷注入、时钟馈通效应更加显著,而较小的开关又由于导通电阻过大,引入一个极点。

图5为本文采用的栅压自举开关,电路原理为:假设采样时钟的高电平等于电源电压VDD,低电平为O,那么电路上电一个时钟周期后,C1,C2均充电到VDD。因此M3的栅极低电平为VDD,高电平为2VDD的方波信号。在ψ为高电平时,M3和M12同时导通,使电容C3充电至电源电压VDD。

此时M10,M7导通,M11的栅极通过M7和M10与地相连,M11处于断开状态。当为低电平时,M10,M3,M12断开,M8,M9导通,这样C2上的电压VDD加到M11的栅源两端,VGS=VDD。因此ψ为高电平时,这个栅压自举开关导通,ψ为低电平时栅压自举开关断开。

在此采样保持电路和前两级MDAC电路的采样开关均采用了上图所示的栅压自举开关。结果显示采用栅压自举后的采样保持电路的线性度大大提高。采用了这样的采样开关后,在输入信号频率范围在50 MHz以内,采样保持电路的SFDR始终能保持在87 dB以上。较高性能的采样保持电路也决定了整个ADC能够较好地工作在欠采样情况下。

2.3 动态比较器

由于采用1.5位/级的结构,即使比较器具有较大的失调误差,数字校正电路还是可以轻易的将这种误差消除,从而保证了结果的正确性。在本设计中,只要比较器的失调误差在200 mV范围之内都可以接受,对比较器的设计要求放宽很多,就极大地提高了设计的灵活性。

动态比较器具有结构简单、功耗小、而且可以内置可调翻转点的特点。但是其缺点是大的失调和回踢噪声。在此所采用的动态比较器结构如图6所示。

图6中M10和M11组成了一个锁存器(Latch),M9和M12用来复位锁存器。M1~M4工作在线性区,相当于可调电阻,当输入信号变化时,左右支路的等效阻抗也会发生变化。当锁存信号Latch为高电平时,处于锁存阶段,M5和M6的漏极分别接到Latch的输出端A点和B点。此时,M7和M8仅起到了一个开关的作用,而M3和M4则有加强Latch正反馈的作用,它们的正反馈增益是由M5和M6源极的电阻来决定的。通过正反馈,源极电阻小的那路输出为高,电阻高的那路输出为低。

比较器的阈值由差分对的电流分配来决定,文献给出了详细的推导,而在实际设计时,常需要通过仿真来设计比较器的阈值电压。而本文中需要的阈值电压为+1/4Vref和-1/4Vref。

仿真结果表明,比较器最高工作频率能够达到300 MHz。蒙特卡罗分析表明,比较器的输入失调在62 mV以内,满足1/4Vref的失调范围要求。

3 性能结果与分析

本文利用运放共享技术设计了一个10位100 MHz的流水线ADC,该ADC的最前端是一个输入带宽很大的采样保持电路,之后的8级MDAC输出利用运放共享技术使用了4个运算放大器,产生16位数字输出。最后一级为一个2位的FLASH模/数转换器。最终产生的18位输出经延迟对准后输入数字修正电路得到最后的10位数字编码。

本设计采用的是TSMC 0.18μm,混合信号1P6MCMOS工艺模型,提供MIM(metal-insulator-metal)结构电容,采用电源电压为1.8 V。使用Spectre进行验证。结果可得在100 MHz采样频率下,采用电容缩放技术后整个ADC电路的功耗为45 mW。

首先输入一个缓变斜坡电压进入模/数转换器,斜坡的变化时间和电路仿真时间必须保证ADC能够每个周期输出增加1位,也就是至少需要1 024个周期。图7为输入斜坡电压后,得到的10个数字码的输出情况。缓变的斜坡电压输入会使得输出每次按照递变的顺序变化,而从图5~图9中可以很明显地看到任意相邻的2个数字码都是按照00-01-10-11的顺序递变。通过观察所有的1 024个数字输出码,未发现任何误码和失码的情况。

图8所示为输入信号为10 MHz(奈奎斯特频率),采样频率100 MHz,采样点数为4 096时的数字输出经Matlab进行傅里叶变换的频谱结果输出,由图可知,SNDR=58.4 dB,SFDR=79.6 dB,此时ENOB=9.5位。

图9所示为采样频率100MHz时SINAD随输入信号频率的变化曲线。可见,在整个奈奎斯特频率内,电路均能达到9位以上的有效精度。ADC各项性能参数如表2所示。

4 结语

本文设计了一个10位100 MHz的低功耗流水线ADC电路。该ADC采用了相邻两级共用一个运放的运放共享技术和逐级电容缩减技术来减小功耗和面积。在输入频率达到奈奎斯特频率范围内,整个ADC的有效位数始终高于9位。在100 MHz采样频率下,电路的功耗仅为45 mW。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多