R1:动态阻抗

C1:动态电容

L1:动态电感

C0:静态电容

CL:负载电容

并行振荡模式的频率可根据以下公式:

FL=[1/2π√(L1*C1))] 2eq eq *√[1+C1/(C0+CL)]

其中[1/2π√(L1*C1))]是晶体串行振荡模式的频率

根据泰勒展开:

FL=[1/2π√(L1*C1) 2eq eq ]*[1+C1/2(C0+CL)] (1)

从公式中可以看出,频率与C0,C1和CL都有关。

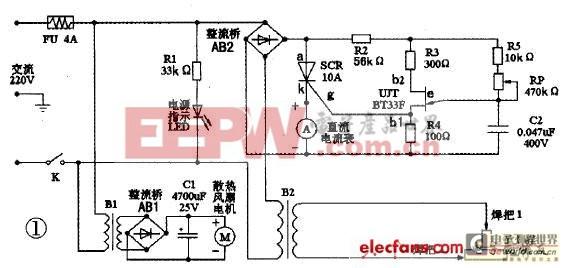

在基频谐振中C1为10-30fF,一般取值为20fF。C0取值与晶体的尺寸有关,一般取值为5pF。但是CL的计算与晶体外接电容和PCB设计和材料有关。下图是参考电路图

图3 晶体外接负载电容示意图

从上面电路中可得出:

1/(C11+CS1)+1/(C12+CS2)=1/(CL) (2)

其中C11,C12是外接电容,也就是线路设计中放在晶体两边接地的两个电容。CS1和CS2是寄生电容,和PCB 电路板的走线,焊盘及芯片的管脚有关。一般为5-10pF(在本文的计算中可设为8pF)。对于C11和C12,没有确定的值(15pF-30pF),这和实际设计有关,例如取18pF。

CL如有变化,并行振荡模式的频率也随之变化,请看图4

APP下载

APP下载 登录

登录

热门文章

热门文章