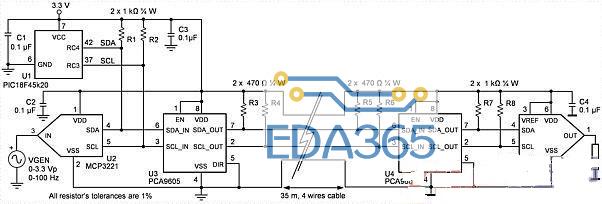

图2.2 (1)静态RAM结构组成原理图

静态RAM的结构组成原理图如图2.2(1)所示,存储体是一个由64×64=4096个六管静态存储电路组成的存储矩阵。在存储矩阵中,X地址译码器输出端提供X0~X63计64根行选择线,而每一行选择线接在同一行中的64个存储电路的行选端,故行选择线能同时为该行64个行选端提供行选择信号。Y地址译码器输出端提供Y0~Y63计64根列选择线,而同一列中的64个存储电路共用同一位线,故由列选择线可以同时控制它们与输入/输出电路(I/O电路)连通。很显然,只有行、列均被选中的某个单元存储电路,在其X向选通门与Y向选通门同时被打开时,才能进行读出信息和写入信息的操作。

图中所示的存储体是容量为4K×1位的存储器,因此,它仅有一个I/O电路。如果要组成字长为4位或8位的存储器,则每次存取时,同时应有4个或8个单元存储电路与外界交换信息,这种存储器中,将列按4位或8位分组,每根列选择线控制一组的列向门同时打开;相应地,I/O电路也应有4个或8个。每一组的同一位,共用一个I/O电路。通常,一个RAM芯片的存储容量是有限的,需要用若干片才能构成一个实用的存储器。这样,地址不同的存储单元,可能处于不同的芯片中,因此,在选择地址时,应先选择其所属的芯片。对于每块芯片,都有一个片选控制端(),只有当片选端加上有效信号时,才能对该芯片进行读或写操作。一般,片选信号由地址码的高位译码产生.

APP下载

APP下载 登录

登录

热门文章

热门文章