遂借其CAN调试工具回来捯饬,久未果 查其为ZLG公司的产品,遂前往之。遇到周立功公司一个大牛,CAN专家,号称没有他解决不了的CAN问题,事实证明,却是有料,周立功公司的CAN 分析仪就是他们一帮人弄的,现在不做研发,转做服务了。拿Can分析仪查之,发现我们的CPU发出的CAN波形 波特率对不上,虽然设置为500K,可是由于CPU时钟频率非常规频率,分频以后,CAN时钟再512K左右,ZLG公司的CAN调试工具是标准品,他们一般要求时序是比较严格的,所以我们的设备跟他的调试工具之间通信通不上,但是网上购买的USB转CAN的调试工具则将SJW域设置的比较大 3或者4 左右,可以跟大部分的CAN通信上,即使是对方的CAN波特率不精确,存在比较大的误差。

CAN问题绝大部分呢,应该就是出在波特率的精确度上,但是一般情况下没有那么精准的测试仪器,所以搞的大家一头雾水。适当调整SJW 同步跳转宽度的大小,可以一定程度的解决这个问题,但是不是最佳的解决方案。虽然现象上看到,哦,通信正常了,我发的包对方可以收到,对方发的数据包我也可以收到,但是,事实是,这里面有了多次的重发,得益于CAN协议,重发,应答等等。

下面简单描述下CAN波特率的分析

比如说500K波特率,一个比特被分为16个时间因子

500K * 16 = 8M

所以CAN时钟应该尽量使8M的倍数。误差尽量小。

同理推算其他波特率跟时钟的对应关系。

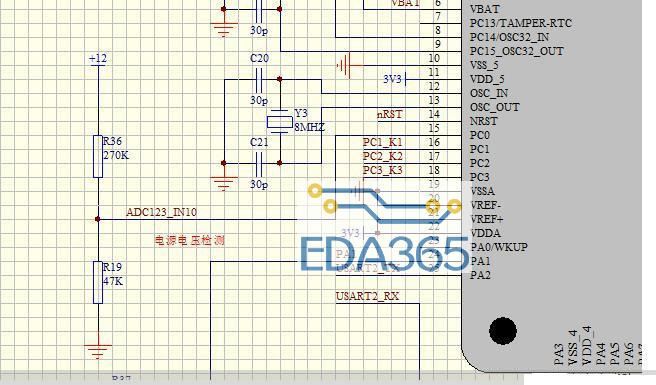

在我们的9263应用中,MCLK = PLLA/2,CAN时钟从MCLK分频而来。

所以PLLA的取值应为16M的整数倍。我们的PLLA一般设置再200M---150M,所以PLLA可取192M 176M 160M等。

WinCE下设置就比较简单了,Eboot启动后,空格可以进入eboot配置菜单,可以直接设置CPU的主频 跟 分频,不赘述。

裸奔的程序 则需要自己去设置倍频跟分频系数,从ATMEL官网下载了PLL计算工具,帮了不上忙,可能没有那么精准,但是尽量接近就好。

#define BOARD_MCK ((16367660 * 98 / 10) / 2) /*160M*/

如上设置为160M的设置

除了这个宏定义的修改以为,在board_lowlevel.c中也需要做一些修改,

#define BOARD_MULA (AT91C_CKGR_MULA & (97 << 16))

#define BOARD_DIVA (AT91C_CKGR_DIVA & 10)

就是那两个系数,注意分频系数不变,但是倍频系数减一了,原因看数据手册就明白。

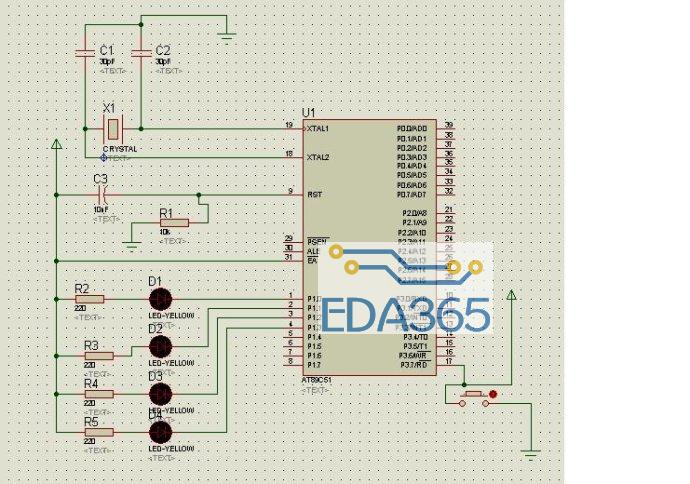

原来以为这样就可以了,可是还有一个地方忽略了,看代码

void LowLevelInit( void )函数中

void LowLevelInit( void )

{

…….

#if !defined(sdram)

/* Initialize main oscillator

初始化主振荡器,时钟等一系列操作

#endif //#if !defined(sdram)

。。。。。。。。。。。

}

整个过程包含在了对sdram宏的判断内,如果定义了sdram则不做下面的处理,乖乖,你不做这个处理怎么可以呢,遂注释掉上面两个宏定义。

这个宏定义不是在文件中定义的,而是在编译器的工程设置里面,

Options-àC/C++ Compiler Preprocessor选项卡,最下面 Defined symbols

也可以直接把sdram去掉。

一直在纠结SDRAM的初始化是在什么地方进行的?

APP下载

APP下载 登录

登录

热门文章

热门文章