MSP430F149有三个时钟源:外部LF(XT1一般为32.768K),HF(XT2一般为8M),内部DCO。从时钟系统模块可得到三种时钟信号:MCLK,SMCLK,ACLK。

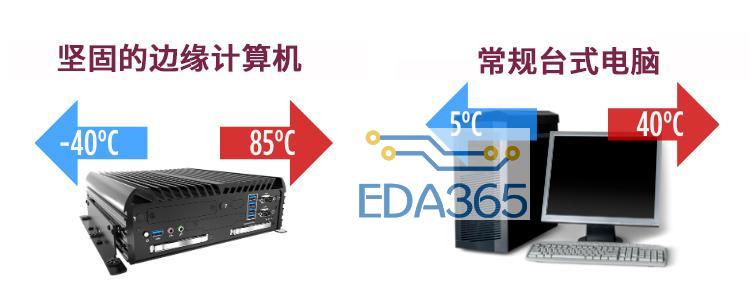

上电默认状况下MCLK,SMCLK信号来自DCO,ACLK来自LF。根据官方PDF说法默认状况下DCO模块配置为RSELX=4,DCO=3,因此DCO应为1M,但示波器实测MCLK/SMCLK为680K,测试温度约25摄氏度。

标注:MCLK主时钟、SMCLK子时钟、ACLK活动时钟。

P5.4,P5.5,P5.6的第二功能分别对应MCLK,SMCLK,ACLK时钟信号,可用示波器测量。测试时发现频率后两位一直在跳动,频率稳定度很差。

MSP430系列单片机选择晶振为时钟源时,时钟周期就是晶振周期。一个机器周期 =一个时钟周期,即430每个动作都能完成一个基本操作; 一个指令周期 = 1~6个机器周期,具体根据具体指令而定。 如果选择8M晶振,则一个机器周期为125ns。51单片机选择12M晶振,它的机器周期是时钟周期/12,一个机器周期为1us,可见 MSP430的的速度是51的8倍。

2、使用方法概述

2.1 程序架构

一般在系统初始化关闭看门狗后要配置系统时钟,配置步骤为:

1、打开晶振;

2、等待晶振起振。清除OFIFG,延时,判断OFIFG是否为0,为0则晶振正常起振,退出判断;

3、选择MCLK/SMCLK时钟源;

uchar iq0;

BCSCTL1&=~XT2OFF; //打开XT2振荡器

do

{

IFG1 &= ~OFIFG; // 清除振荡器失效标志

for (iq0 = 0xFF; iq0 > 0; iq0--); // 延时,等待XT2起振

}

while ((IFG1 & OFIFG) != 0); // 判断XT2是否起振

BCSCTL2 =SELM_2+SELS; //选择MCLK、SMCLK为XT2

2.2 细节描述

对于DCO可以通过配置电阻和DCO得到不同的频率。电阻可配置片内或片外(DCOR一般片内),片内电阻有8中选择(RSELX),DCO有8中选择(DCOX)。

3、相关寄存器

1、DCOCTL

DCOx Bits

7-5

DCO frequency select. These bits select which of the eight discrete DCO

frequencies of the RSELx setting is selected.

2、BCSCTL0

XT2OFF Bit 7 XT2 off. This bit turns off the XT2 oscillator

0 XT2 is on

1 XT2 is off if it is not used for MCLK or SMCLK.

RSELx Bits

2-0

Resistor Select. The internal resistor is selected in eight different steps.

The value of the resistor defines the nominal frequency. The lowest

nominal frequency is selected by setting RSELx=0.

3、BCSCTL0

SELMx Bits

7-6

Select MCLK. These bits select the MCLK source.

00 DCOCLK

01 DCOCLK

10 XT2CLK when XT2 oscillator present on-chip. LFXT1CLK when XT2

oscillator not present on-chip.

11 LFXT1CLK

SELS Bit 3 Select SMCLK. This bit selects the SMCLK source.

0 DCOCLK

1 XT2CLK when XT2 oscillator present on-chip. LFXT1CLK when XT2

oscillator not present on-chip.

DCOR Bit 0 DCO resistor select

0 Internal resistor

1 External resistor

4、实例

4.1 配置MCLK/SMCLK

见本节2.1。

4.2配置DCO

void main(void)

{

WDTCTL = WDTPW +WDTHOLD; // Stop Watchdog Timer

DCOCTL = DCO0 + DCO1 + DCO2; // Max DCO

BCSCTL1 = RSEL0 + RSEL1 + RSEL2; // XT2on, max RSEL

BCSCTL2 |= SELS; // SMCLK = XT2

P5DIR |= 0x70; // P5.6,5,4 outputs

P5SEL |= 0x70; // P5.6,5,5 options

while(1)

{

}

}

实测DCO最低128K,最高4.58M。

APP下载

APP下载 登录

登录

热门文章

热门文章