这是arm的时钟集成模块,主要想介绍关于arm的时钟体系.

S3C2440 有2个PLL(锁相环),一个是mpll,一个是upll

pll(锁相环)

是一种产生时钟频率的东西,通常产生时钟频率都是使用晶振(晶体振荡器),不过由于频率固定或者生产成本高等一系列的原因,才产生出pll。pll合成器有外部晶体和对晶体的特定频率加班或者分频的集成pll电路。可以看出,pll可以在本身晶体的限制下自己diy要的频率,而且相对成本也不会很高。

mpll会产生3中种时钟频率:FCLK,HCLK,PCLK

FCLK(CPU的频率):主要用于cpu核

HCLK:用于AHB(高速的外设总线)

PCLK:用于低速外围设备总线

upll用于usb外设

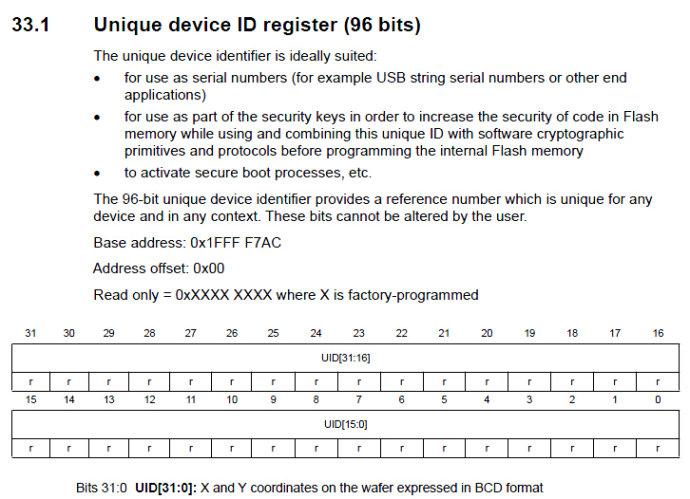

左上角的那个圈中的EXTCLK与OSC这两个是arm的时钟来源,EXTCLK是外部时钟,OSC是晶体。通过OM[2:3]来决定是用哪种方式;

这幅图让我们知道了arm时钟的产生来源,以及一系列的过程.

当arm通电的使用,FCLK不是有mpll来决定的,而是有FIN(外部输入时钟),当nRESET高电平的时候,PLL开始进行设置,这个时候OM[2:3]已经锁定了,"PLL is configured by S/Y first time" 这个地方就是PLL的寄存器都已经被设置好的时候,至于LOCKTIME是什么,这个是PLL要输出稳定的频率所需要的时候,这个时候的FCLK为0,也就是cpu这个时候是不工作的。等locktime时间玩了以后,我们看到FCLK的频率就变的高很多,这就是cpu频率的来源。

APP下载

APP下载 登录

登录

热门文章

热门文章