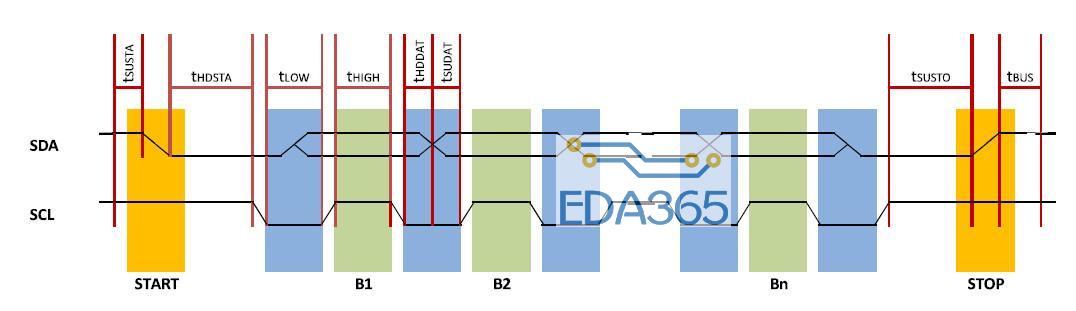

1、所谓边沿检测,就是检测输入信号或FPGA内部逻辑信号电平的跳变,即实现上升沿或下降沿的检测,捕获到以后以此用作使能信号(简单可理解为:一旦检测到这个信号,则发生什么什么),来作为时序逻辑的触发信号。总之,在基础中,这个还是很重要的,在后面的串口和SPI接口中都要用到。

(一)、一级寄存器

从一级寄存器中很好理解下降沿和上升沿的检测:a和b都是从trigger来的(三者一样),只是b比a在时间上迟了一个寄存器的时间。现在假设0时刻到了,trigger到a了,但是还没有到b,到了寄存器,被寄存了;等待下一个时刻1到来,a走了(不用管了),来了一个新的叫c,同时,b从寄存器得到了之前寄存的,那个现在的1时刻,有了两个信号,b和c,而且b是前一个时刻的,而c是现在时刻的(谁先谁后这点很重要)。所以:

下降沿neg_edge=b&~c;

由上图可以看出,当下降沿来的时候,c取反再与上b,得出输出为1;反过来想,输出neg_edge为1的时候就表示检测到下降沿了。

上升沿pos_edge=~b&c;

同理。当pos_edge为1,表示检测到上升沿。

(二)两级寄存器

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c<=1'b0;

d<=1'b0;

end

elsebegin

c<=s;

d<=c;

end

assignneg_edge=d&!c;

assignpos_edge=!d&c;

endmodule

为了在波形图中能看到c、d寄存器,把程序修改为

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge,

c,//为了观察c和d的波形而添加的

d//为了观察c和d的波形而添加的

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

outputc,d;//为了观察c和d的波形而添加的

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c<=1'b0;

d<=1'b0;

end

elsebegin

c<=s;

d<=c;

end

assignneg_edge=d&!c;

assignpos_edge=!d&c;

endmodule

测试文件如下:

`timescale1ns/1ns

`defineclk_period20

moduleedge_tech_design_tb;

regclk;

regrst_n;

regs;

wireneg_edge;

wirepos_edge;

wirec,d;//为了观察c和d的波形而添加的

edge_tech_designedge_tech_design

(

.clk(clk),

.rst_n(rst_n),

.s(s),

.neg_edge(neg_edge),

.pos_edge(pos_edge),

.c(c),//为了观察c和d的波形而添加的

.d(d)//为了观察c和d的波形而添加的

);

initialclk=1;

always#(`clk_period/2)clk=~clk;

initialbegin

rst_n=1'b0;

s=1'b0;

#(`clk_period/4)

#(`clk_period)

rst_n=1'b1;

s=1'b1;

#(`clk_period*5)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*3)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*5)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*3)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period*3)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period)

$stop;

end

endmodule

在仿真图中可以看到这样的图形(街区图中下降沿部分一小段)

输入信号s从高变成低的时候,出现下降沿,然后等到时钟clk的上升沿到来,s传输到c,d还没传输到,被寄存在d之前的寄存器内,等待第二个时钟上升沿到来,寄存器中的信号传输到d了,此时根据

neg_edge=d&~c;

可以得到neg_edge的波形。

APP下载

APP下载 登录

登录

热门文章

热门文章