虚拟仪器,就是在通用计算机平台上,用户根据自己的需求定义和设计仪器的测试功能,与传统仪器相比,虚拟仪器在智能化程度、处理能力、性能价格比、可操作性等方面均具有明显的技术优势。

本文将着重介绍一种新型优良的下位机—基于USB2.0的高速数据采集卡在虚拟仪器中的应用。

本文重点分析的下位机即智能A/D,是虚拟仪器硬件设备中的关键环节。下位机通过特定接口接受来自上位机的指令并向上位机提供自身所处的状态:在收到采集指令后,对传感器发送的模拟电信号进行A/D采样以转化为数字信号,然后将数字信号通过USB接口传给上位机。

本系统的下位机支持2个通道的传感器信号进行A/D转换,其最高采样效率为120MHz,采样转换精度为8位,系统采用了一个内含先进先出(FIFO)内存的USB2.0控制芯片,该内存用于存放A/D转换后的数据,使用FIFO可以有效地缓冲采集数据,减少频繁的指令传送,使上位机有更多的时间进行其他处理,并且不容易丢失数据。该下位机可以编程控制采集频率和采样增益,具有较大的灵活性。

基于USB2.0的高速

数据采集卡

硬件系统

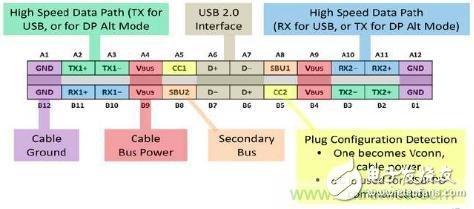

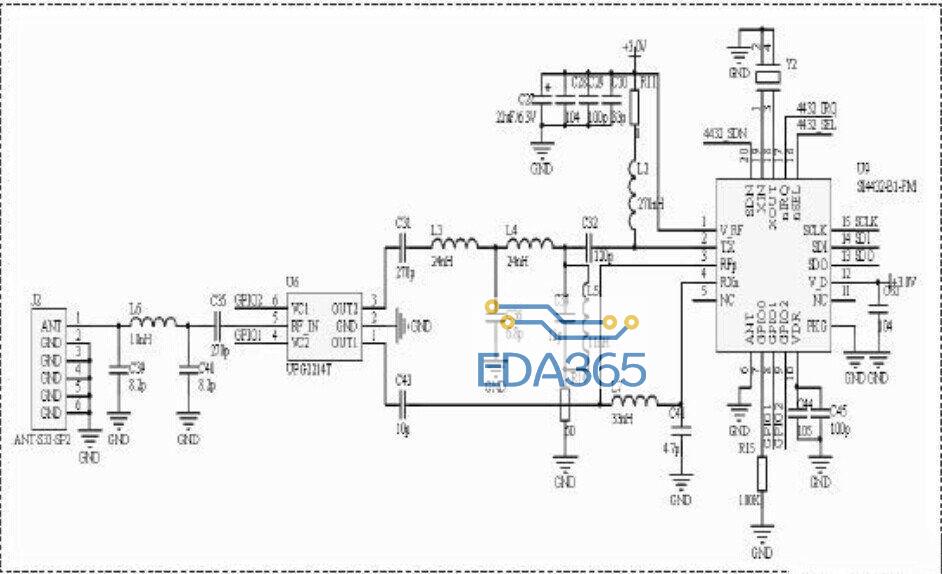

虚拟仪器硬件的核心部分是USB设备接口模块,其功能是由硬件和软件共同来完成的。USB接口示意图如图2所示。下面介绍一下主要功能模块器件的选择和功用。

ADC的选择

本设计中选用了AD9059。该器件是8位单片双通道ADC,具有高速、高性能、低功耗及易使用等特性,60MSPS的编码速率和120MHz的最大功率模拟带宽使其在多路数据采样系统中表现出优秀的动态性能。大部分情况下,AD9059仅需要一个单极性的5V电源和一个编码时钟即能正常工作。编码时钟提供与TTL/CMOS兼容的逻辑数据输出,并控制两个A/D转换通道同时对数据进行采样。如长时间不需要采集数据,可启动休眠模式使总功耗小于12mW。ADC的时钟及控制信号等由CPLD提供。

CPLD的选择

在高速数据采集卡中,时序复杂而且精细,可能会因为一个门的时延,而导致整个硬件电路的失败。所以在本设计中采用了CPLD来实现电路的数字控制功能。

CPLD主要任务是负责在EZ-USB FX2(即CY7C68013)处于Slave FIFO模式时实现读/写控制信号、时钟、输出使能、端点的选择以及对放大器和ADC的控制等功能。?

基于CPLD容易开发升级的优点,在本设计中,所有的数字电路部分,全部是在CPLD内实现的,本设计采用了Lattice公司的ISP1032芯片,所用的EDA软件是Lattice公司的ispEXPERT系统,编程语言为ABEL语言。

经过在实践中检验,在高速数据采集卡中,用ISP1032来实现数字逻辑电路功能,可以使高速数据采集卡工作稳定,各方面性能良好。

信号调理模块

在高速数据采集系统中, 现场输入信号是高频的模拟信号,信号变化的范围都比较大,如果采用单一的增益放大,那么放大以后的信号幅值有可能超过A/D转换的量程,所以必须根据信号的变化相应地调整放大器的增益。在自动化程度较高的系统中,希望能够在程序中用软件控制放大器的增益,经过考虑本文选择具有增益可编程功能的芯片—AD8321。该芯片具有频带宽、噪声低、增益可编程且易于与单片机进行串行通信等优点,十分适合在数据采集系统做前置放大。程控放大模块的的控制字可在labview设定,再经过USB接口由EZ-USB FX2传给AD8321。

APP下载

APP下载 登录

登录

热门文章

热门文章