摘要:本文设计了一种符合手机电视T-MMB标准的信道译码解决方案,并进行了MATLAB仿真和FPGA的实现。同时针对部分并行结构的准循环低密度校验(QC-LDPC)码译码器,提出了基于块RAM的高效存储方法。该方法既可以同时读取用于运算的校验节点信息或变量节点信息,又可以实现在同一块RAM中存储不同子矩阵对应的校验节点信息或变量节点信息,不仅避免了块RAM资源的浪费,而且减少了译码器实现所需的存储资源数量。在Xilinx公司Virtex-4系列的FPGA上的实现结果表明,与传统的子矩阵与块RAM一对一存储的译码结构相比,本文提出的QC-LDPC码译码器设计方法能够在减少块RAM数量的同时有效地提高系统的时钟频率和译码吞吐量。

引言

随着移动网络的迅速发展,移动多媒体广播业务已经成为炙手可热的发展热点。国际上流行的数字移动多媒体广播标准主要有三个:欧洲的DVB-H,美国的MediaFLO和韩国的T-DMB。而中国在2006年9月,由北京新岸线软件科技有限公司提出了新一代地面移动媒体广播(Terrestrial Mobile Multimedia Broadcasting,简称T-MMB)系统。该系统具有独立自主知识产权,相比于其他制式具有频谱利用率高、复杂度低、功耗小、频点可用性好、兼容性好等优点[1]。T-MMB系统是基于多载波OFDM调制的无线通信系统,采用LDPC码作为信道编码技术,无需级联外码就可以保障系统的接收性能,从而提高了系统的频谱效率,降低接收机复杂度[2]。

低密度校验(Low-Density Parity-Check,LDPC)码是一种基于稀疏校验矩阵的线性分组码,具有逼近香农极限的译码性能[3,4]。准循环低密度校验(QC-LDPC)码是低密度校验码的一种,其生成矩阵和校验矩阵都具有准循环的特点,在保持较好译码性能的基础上大大降低了译码器实现的复杂度,易于用FPGA实现。LDPC码译码器的研究工作一直是LDPC码研究的一个重要方向。

LDPC码的译码是一个不断迭代的消息传递过程。译码过程中需要存储大量的信息,包括各节点的初始信息、外信息和后验信息等[5]。LDPC码较强的纠错性能一般是建立在较长码长基础上的,这会增加译码算法实现过程中的存储器容量,增加硬件资源成本与开销[5]。为了有效解决LDPC码译码器的高存储量问题,本文在QC-LDPC码基础上,基于归一化最小和译码算法,设计出一种能够有效降低存储量的译码器结构,并应用FPGA实现。与传统的译码器相比,本文提出的译码器结构能节省75%的存储空间,同时提升系统的时钟频率和译码吞吐量。

T-MMB系统的总体设计

本文搭建的T-MMB系统总体架构如图1所示。按照图1建模,进行MATLAB仿真并进行译码器的FPGA实现。业务数据经过1/2码率的LDPC码编码后,得到调制前的信息序列,其中T-MMB系统中LDPC码有两种编码方式,表1给出了标准中LDPC码的详细编码参数;之后进行8PSK调制,加高斯白噪声;之后解调得到各码元对应的软信息;最后,按照译码算法进行译码处理,求出误码率。本文采用的译码算法为归一化最小和译码算法,它是修正最小和译码算法中的一种,可以避免译码过程中的信道估计,提高译码器工作的稳定性[8],其译码步骤参考文献[5]所示。

高效存储译码架构

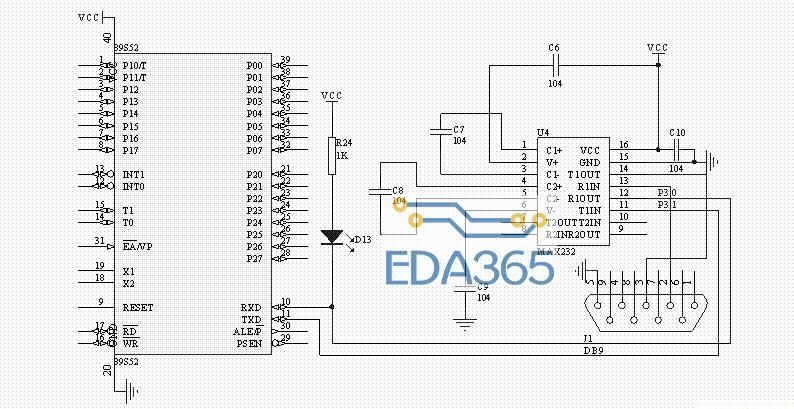

手机电视标准T-MMB中规定QC-LDPC码的校验矩阵维度为2304×4608,可以由32×64个72×72的分循环矩阵构成。每行中不为全0矩阵的个数为7,每列中不为全0矩阵的个数为2、3、9。综合考虑译码器的速率要求和FPGA面积要求,本文采用部分并行结构的运算方式完成译码器的设计,采取8bit均匀量化。按照文献[9]对存储资源的计算方法可知量化比特数Q=8,部分并行结构译码器的复用指数L=72。水平运算时有32个校验节点处理单元(CNUs)同时运算,需要同时向32×7个存储变量节点信息的RAM中读取变量节点信息用于水平运算,计算结果需要同时存储到32×7个存储校验节点信息的RAM中,重复计算72次就可以完成一次迭代中的水平运算。垂直运算时有64个变量节点处理单元(VNUt)在同时运算,向每列中的子矩阵对应的存储校验节点信息的RAM同时取出数据进行运算,运算72次后将结果存储到相应列矩阵对应的存储变量节点信息的RAM中。

若采用传统的子矩阵存储方式,每个子矩阵需对应一个RAM存储校验节点信息以及一个RAM存储变量节点信息,每个RAM宽度为8bit,深度为72。本次设计共需要448个RAM来存储校验节点信息以及变量节点信息,需要占用较多的存储资源,同时由于本设计LDPC码码字较长校验矩阵较大,其余单元在实现时亦需要占用较多的存储资源,一般的FPGA很难满足这样的要求。

本文设计了一种新的RAM存储方式,采用Xilinx公司Virtex-4系列的FPGA进行实现,采取自带块RAM的存储方式,RAM容量为18Kb。在实现时,将块RAM例化为宽度32bit深度155的双口块RAM,深度0~71上存放校验节点信息,深度80~151上存放变量节点信息。因为校验节点与变量节点同时处理的多个消息必须同时读出或写入存储器中[10]。为保证同步,本文采取的做法是将偏移量相同的子矩阵对应的校验节点信息或变量节点信息存储到同一块RAM中。由于Xilinx的块RAM最大位宽为32bit,所以最多有4个子矩阵对应的信息可以存储到同一块RAM中。存储方式如图2所示。

APP下载

APP下载 登录

登录

热门文章

热门文章