1 引 言

USB ,是英文Universal Serial BUS(通用串行总线)的缩写,而其中文简称为“通串线,是一个外部总线标准,用于规范电脑与外部设备的连接和通讯。是应用在PC领域的接口技术。USB接口支持设备的即插即用和热插拔功能。USB是在1994年底由英特尔、康柏、IBM、Microsoft等多家公司联合提出的。

随着半导体工艺技术的发展,集成电路设计者能够将愈来愈复杂的功能集成到单硅片上。SoC是将系统集成在一块芯片上,包括微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)等。SoC的一项关键技术即为IP(Intellectual Property)复用技术。IP核是指在电子设计中预先开发的用于系统芯片设计的可复用构件,系统设计者在进行一个复杂设计时将众多IP核在一个芯片上有效集成,从而构成一个功能强大的系统。

在设计IP核时应注意其可重用性,为了增强IP核的可能重用性,使IP核能更好地适应不同总线结构的SoC平台,可以为IP核设计一个总线接口模块。该模块主要完成片上总线的协议转换和实现,称之为总线适配器(BusAdapter)。其特点为:IP核与外部的片上总线标准无关,其逻辑相对固定,只需对相应的总线适配器进行配置就能够有效地集成于不同片上总线的SoC平台。当前SoC中常用的总线协议有三种分别是:ARM公司的AMBA、Silicore公司的WISHBONE SoC Interconnection Archi—tecture和Ahera的Avalon总线。

本文实现的USB IP核中,设计了总线适配器,在综合前针对WishBone总线或AMBA ASB总线通过宏定义进行设置,从而使USB IP核能够直接集成于WishBone或AMBA ASB总线的SoC系统中。

2 USB系统组成部分

系统主要分为三个部分:主机、设备和互连。在任何的系统中,只有一个主机,与主机系统的接口称作主机控制器。他可由硬件、固件和软件综合实现。设备可以分为功能性设备即外设和集线器,前者作为系统的功能扩展设备而后者作为设备的扩展连接点。互连定义了主机和外设的连接和通信方式。包括总线拓扑结构、内部分层关系、数据传输模型和总线访问控制等几个部分。一个简单的系统可以由一台主机和一个外设构成。

3 USB的模块设计

3.1 模块划分

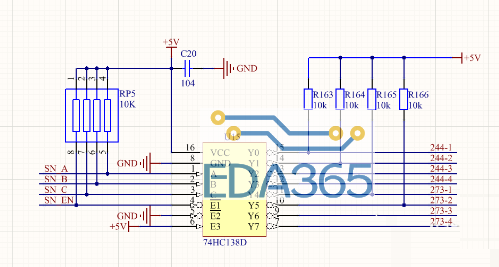

USB IP核主要是实现了USBl.1协议,在对整个协议分析的基础上,整个IP核共分成五大模块:串行接口引擎模块、协议层模块、端点控制模块、端点存储模块和总线适配器模块。串行接口引擎主要是支持最底层的USB协议,由于USB协议中为了增加抗干扰对比特流进行了“不归零码(Non Return to Zero Invert)”的编解码,同时为了可以从比特流中提取同步信号用了“位填充”和“位剔去”。串行接口主要完成比特流方面的处理。协议层模块则主要是完成解包和打包。在USB协议中,数据缓冲区用了端点(Endpoint)这个概念,不同的缓冲区用了不同的端点号来区分,端点存储模块就是相应的数据缓冲区。端点控制模块主要是端点控制寄存器和端点状态寄存器,对端点进行相应的控制。总线适配器模块主要是在不同总线结构的SoC中,对USB IP核总线接口进行相应的配置,从而可以进行无缝连接到相应的SoC中。USB IP核模块划分如图1所示。

3.2 串口接口引擎

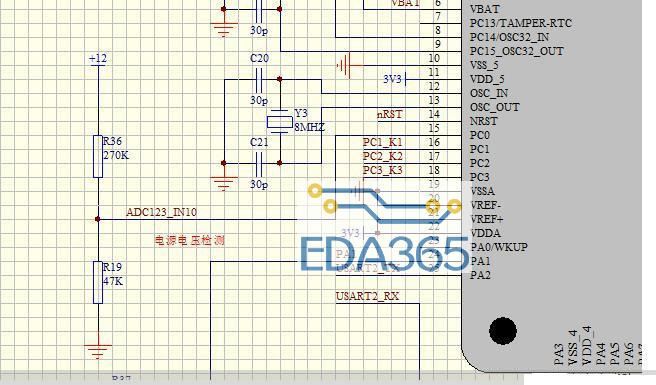

串口接口引擎主要是完成USB协议中比特流的处理。根据数据的传输方向可分为发送部分和接收部分。发送部分即为USB设备给USB主机发送数据,接收部分则为USB设备从USB主机那里接收数据。如图2所示。

接收部分:从同步域中恢复出12

MHz的时钟信号,接收主机过来的比特流对其进行不归零码(NRZI)解码,剔除位填充然后进行串并转换,最后将转换后的数据以字节的形式传给协议层。接收部分还要能判断出一个包的开始,在USB传输过程中,是以包为单位的,因此接收部分首先要测包的开始SOP(Start

of Packet),所有包都是从同步字段(SYNC)开始的,同步字段是产生最大的边缘转换密度(Endge Transition

Density)的编码序例。以NR—ZI编码的二进制串“KJKJKJKK”同步字段最后2位是同步字段结束的标记,同时标志了包标识符(Pacekt

Iden一tiler,PID)的开始。只有当检测到包SOP才开始后面的NRZI解码、去位填充和串并操作,否则就继续处于等待阶段。

在接收部分还需要有检错部分,在检查到传输过来的数据有错误时,要进行相应的错误处理。如在NRZI解码后,在对数据进行去位填充时发现了有连续7个“1”则可以认为数据在传输过程中出现了错误,数据包已经损坏,必须通知协议层。在接收部分需要特别注意的是:在接收USB主机过来数据时,是不同的时钟域,因此必须考虑到亚稳态问题。在本设计中,由于只处理单个比特信号,因此用了两级寄存器来消除亚稳态。

发送部分:将协议层打包好的加上同步字段,然后进行并串转换,将字节形式转换成比特流形式,接着根据协议将数据进行位填充和NRZI编码,通过D+和D一信号传送给USB主机。这个同步字段也是告诉USB主机有一个新数据包发送过来了,在发送部分还要产生包结束EOP(End of Packet)的信号。

APP下载

APP下载 登录

登录

热门文章

热门文章