包括Analog Devices公司的ADV7179 DAC在内的许多视频器件都带有PAL和NTSC视频信号专用模拟基带电视接口。遗憾的是,这些类型的DAC只接受隔行扫描图像格式的视频,而你也许需要逐行扫描视频。而且,许多逐行扫描图像的大小有所不同,这使得更难以把逐行扫描图像转换成隔行扫描图像。因此,你需要一个注入SDRAM或DRAM之类的通用高效图像缓冲器,作为图像场隔离策略。

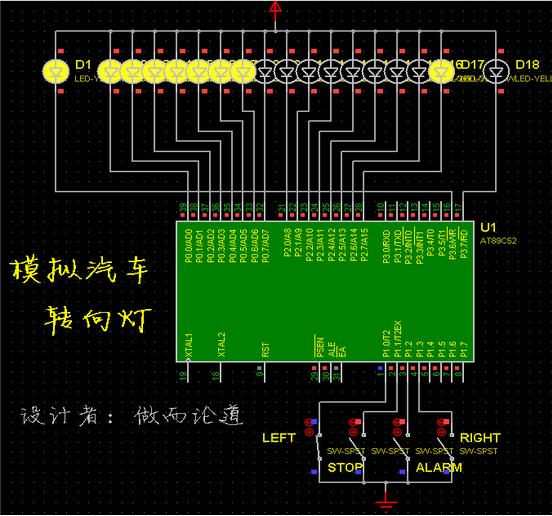

图1为某种典型逐行扫描图像格式的时序。上方的四个信号包含逐行扫描图像源,其中包括一个帧同步信号、一个行同步信号、一个信号,以及一个带有像素图像数据的像素时钟。下方的两个信号是帧同步信号和行同步信号,其中前者在高电平时,会包含许多行同步信号。

图1,像素时钟信号把图像数据放入FIFO存储器中,这些数据随后同步,并进入系统RAM中。

像素时钟把逐行扫描图像数据写入FIFO存储器中。当每个行同步信号均为低电平时,一个速率更高的数据时钟随后能够把数据写入RAM中。无论像素时钟由于各种逐行扫描图像数据尺寸而如何变化。这一规程确保了逐行扫描图像数据将正确写入SDRAM中,当RAM写使能信号或RAM读使能信号为高电平时,系统把数据写入SDRAM中或从中读出数据。

图2为逐行扫描图像数据的帧同步信号和隔行扫描图像数据的帧同步信号。低电平时,在逐行扫描图像数据的每个行同步信号都会执行写新数据使能与读老数据使能信号,而在高电平时,在每个帧同步信号都会执行该使能信号。但你可以只在帧同步信号为低电平时执行读老数据使能信号。在该期间不存在有效图像数据时。图3为SDRAM读写规程的数据流。例如一个帧可能包含15行,你在其中把行数据定义为00至0e。奇数行的图像数据为1、3、5、7、9、11、13、15,偶数行的图像数据为2、4、6、8、10、12、14。

图2,逐行扫描图像数据的帧同步信号交替读取存储器中的奇数行数据和偶数行数据。

利用上述SDRAM读写策略,你可以生成隔行扫描数据,并使之与原始逐行扫描数据的帧同步信号同步。因此,你无需担心图像大小。而且,它能轻松调节隔行扫描图像数据时序,改变空白行数量,并且不改变写SDRAM序列或读SDRAM序列。你只需确定低电平期间的哪个行同步信号从SDRAM读取老图像数据。

图3,帧同步信号的状态决定系统是执行读操作还是写操作。

APP下载

APP下载 登录

登录

热门文章

热门文章