嵌入式系统除错的工作量,可望占了嵌入式软体专案工作量的一半以上。了解硬体除错功能以及它们所能解决的问题,是选择正确的晶片、建立除错系统以及提高生产效率的关键。

很多人都相信臭虫(bug)此一用词起源于海军少将 Grace Murray Hopper。但事实上,没人知道这种用法的真正来源,它可能可以回溯到 Thomas A Edison,或甚至更早。美国海军后备役军官 Hopper 在 1945 年 9 月 9 日于哈佛大学对 Mark II Aiken 继电计算器( Relay Calculator)进行测试时,于短路的 Panel F #70 号继电器处发现了一双臭虫。她把这只臭虫拿掉后(就是对电脑进行除臭虫(debugging)),就解决了这台机器不定时关机的故障(参考文献 1)。虽然这个早期的例子指的是从系统硬体中去除臭虫,但今天debugging这个词是指发现一个程式的问题,并去掉缺陷代码(defective code)的过程。这些问题包括任何与原始意向的差异,而去掉缺陷代码的做法则远优于增加纠正代码(correction code)。理想情况下,在任何时间都可以获得所有的特性(如系统的R流排与暂存器值),供监控与修改。但随着 IC 转向 SoC,可存取性(accessibility)就变得更加困难了。

对硬体除错,是要尽可能地可以存取到嵌入式系统内部资源,这可以透过观察系统的特性,如 CPU 状态和 PC 值,或修改系统的参数。在嵌入式系统设计的早期可以用简单技术进行除错,如记录(logging)与监控,或者对多核心 SoC而言,可以采用最新开发的方法,如跟踪、缓衡记忆体除错(cache debugging)和交叉触发(cross-triggering)等。本文的重点不是在如何编写代码或为代码除错,而是描述现在可用的嵌入式硬体硅智财权(intellectual property ,IP),以及该 IP 能解决哪方面的除错问题。

记录与监控

最古老也是最常用的除错方法就是在代码中增加一些列印叙述(print statement),它可以显示软体某个部分的执行资讯,并提供暂存器和变数的实际值。这可能是一年级学生练习hello world的一种延续,该程式会在荧幕上显示这两个词,用于表示程式能够运行,以及执行到了某个点。列印叙述(或 printf 语句)只是记录的一种变型,它是用处理器将重要资讯写入一个管道(pipe),作为外部跟踪的过程。所使用的管道将视系统而订,在 printf 情况下,管道是标准的输出(荧幕),但它也可以是 UART、USB,甚至是通用 I/O。

当你需要用一种对程式设计工程师有意义的方式,组织各个部分资讯时(例如提供感测器资讯或状态机的转换),采用记录的方法是很有价值的。可以用记录工具来分析记录的资讯,并产生一个后处理资料库。必须小心使用记录功能才能获得高效率。例如,记录资讯应使用关键字开头,如警告、错误或除错等,并应能识别出资讯的建立者。应将记录功能划分为一小组档案,以便于维护,并提供时间戳资讯。不幸的是,记录是一种侵入性的方法,它会修改软体的即时状态,因而不同于最终应用。

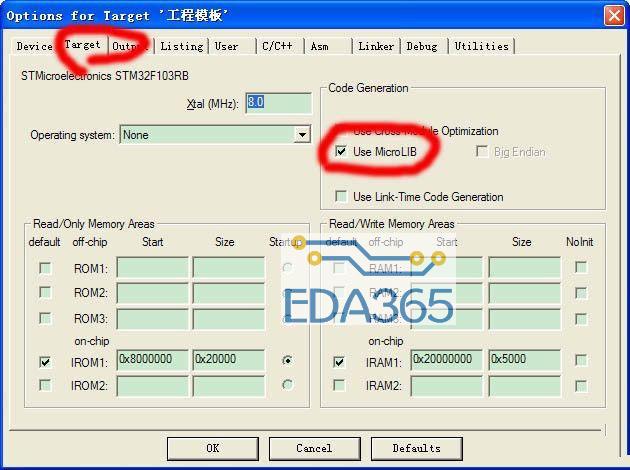

除错监控器是另一种常见的除错工具,它与运行在 CPU 记忆体中的目标代码一起工作(参考文献 2 和参考文献 3)。除错器运行在一台主机上,它透过一个专用的埠发送指令和接收响应,从而达到与监控器通信的目的。可以将 Linux 上的 gdbserver 程式当作一个除错监控器,不过它比早期的 ROM 监控器更复杂

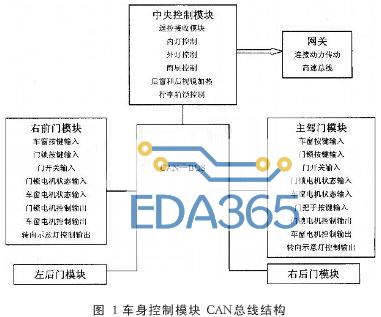

(图 1)。

当使用者希望在某条指令处设置一个中断点时,gdbserver 会保存该指令,而用一个系统呼叫(system call)来替代它。Gdbserver 然后用 Linux 的 ptrace 程式获得所有进行系统呼叫的应用程式资讯。接着,当发生系统呼叫而⒍中断点时,gdbserver 可以取得对被除错应用的控制。除错器运行在一台主控机上,透过串列埠或乙太网路连接到目标物件(参考文献 4)。监控器的方法既便宜又实用,但也有一些缺点,例如需要在进行任何除错前载入代码,并可能与应用软体相互影响。如果代码位于快闪记忆体中就不能使用监控器软体,因为要插入软体中断点就需要修补应用软体。

内电路模拟

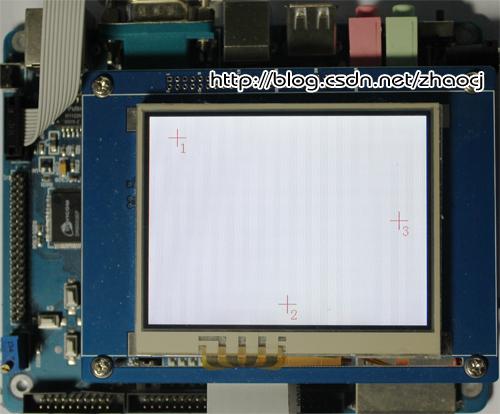

内电路模拟器(in-circuit emulator ,ICE)是第一种以硬体为基础的除错技术,它是所除错处理器的一个版本。ICE 通常使用一颗现场可编程闸阵列(field-programmable gate array,FPGA)。FPGA 外合(bond out)其内部R流排和状态信号,而让使用者可以使用它们(图 2)。

ICE 提供的除错功能多于 ROM 监控器。使用 ICE 时,必须用一个连接到 ICE 盒的连接替换待除错电路板上的处理器。一个运行并模拟除错器功能的主机控制这个 ICE 盒。ICE 的主要局限性之一是它的价格昂贵。另外,虽然这个方法很适合简单的处理器,但现代 SoC 有更高的复杂性、整合度和频率,因此 IC 供应商难以为现代处理器提供 ICE 版本。

一些欧洲公司在1985 年成立了联合测试活动组(Joint Test Action Group,JTAG),这个联盟尝试要解决测试半导体 IC 的各种问题。它们为 IC 的边界扫描测试建立了 IEEE 1149.1 标准,并在 1990 年公布了此一标准(参考文献 5 和 图 3)。

JTAG 标准定义了一个有限的 I/O JTAG 埠,有多达五个信号,透过串列通信完成电路的测试与分析:测试时(test clock,TCK)、测试模式选择(test-mode select,TMS)、可选的测试重定(test reset, TRST)、测试资料登录(test-data in ,TDI)和 测试资料输出(test-data out,TDO)。

IEEE 将 JTAG 硬体建立在一个 16 态的有限状态(finite-state)机上,并由 TMS 信号控制。TCK的上升沿时(rising- edge clock)X取到此一 TMS 信号。资料资讯在TDI 垫(TDI pad)移入,并在TDO 垫移出。最后用 TRST 来对设计重新设定。IC 的每个垫都可以增加扫描暂存器,并将它们内部连接起来构成一个边界扫描链。可以透过 TDI/TDO 和 JTAG 命令将此链移入和移出,以测试电路板上的外部连接,测试 IC 内部的逻辑连接,X取 IC 垫的值,并将 JTAG 置于旁路模式。JTAG 提供了低成本的u造测试功能,并成为最常用的测试方法。但是,由于它有易于使用、高可用性和低成本实现的特点,设计者经常会把 JTAG 当作除错埠,以存取片上的除错资源(参考文献 6)。

APP下载

APP下载 登录

登录

热门文章

热门文章