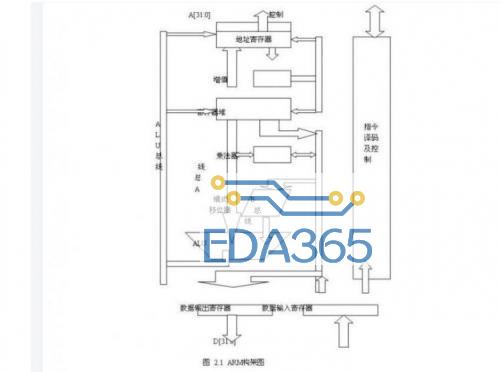

DSP+FPGA混用设计

为了提高算法效率,实时处理图像信息,本处理系统是基于DSP+FPGA混用结构设计的。本系统要求DSP可以满足算法控制结构复杂、运算速度高、寻址灵活、通信能力强大的要求。所以,我们选择指令周期短、数据吞吐率高、通信能力强、指令集功能完备的DSP。选用百万门级FPGA进行硬件实现。非常适合实时信号处理系统。

系统架构设计

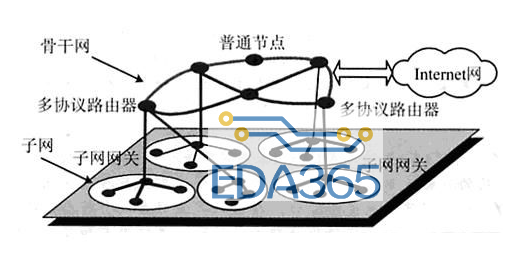

CompactPCI作为PCI总线的电气、软件和工业组装标准,是当今最新的计算机标准之一。CompactPCI总线的高速、坚固、可靠、稳定,与PcI软件的良好兼容性,使得它成为工控领域最流行和通用的计算机接口总线。

CPCI目前最高传输速度528MB/s,可用的PCI-X的最高传输速度可达1066MB/s。

在高速坚固,可靠稳定的技术基础上,本系统设计了可运用客户自有协议的CPCI背板和接口统、高度模块化的CPCI业务板。

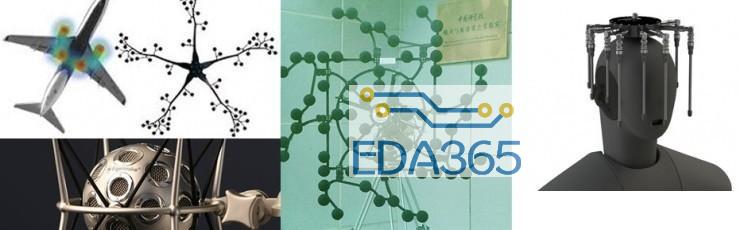

综合业务处理平台

综合业务处理平台是指在单一平台实现多路信号预处理、复杂图像算法、图像显示、数据存储、系统控制等任务。这不仅要求硬件必须具备高性能,可以进行实时处理,同时,嵌入式的应用环境还要求体积小、重量轻、功能强、可靠性高。

完整的系统由以下几个模块构成:箱体,电源,背板,A/D预处理板与信号处理板等。

箱体,电源和背板

箱体采用标准19英寸上架的外型尺寸。内部空间:支持2U 4槽CPCI背板;支持2个3UCPCI电源。箱体背部双电源输入接口,通断式开关(支持常开)。以便响应断电后系统重启的要求。

3U CPCI电源支持热插拔;采用和系统一体的智能管理电源背板;支持AC输入。

背板上有4个6U插槽,每个插槽有5个插座:P1,P2,P3,P4,P5。P1,P2为标准PCI,提供5V/3.3V信号环境。

系统槽P3,P3,P5定义按照系统板MIC-3369定义标准。

扩展槽:P1,P2,P3,P4,P5采用穿透型长针,前后穿透,配护套。P1,P2这样设计,前插板和后插板都可以根据实际需求从背板上取得供电。P3,P4,P5提供完善的信号前后路由。

此外,3个扩展槽的P3之间、P4之间、P5之间设计为PIN TO PIN连通。

这样设计,为业务板间建屯线性扩展,上一级处理模块与下一级模块通信建立了物理通信端口。

A/D预处理板

考虑到系统每个业务板都要处理多路输入,而且工程安装设备要求便利,我们专门为模拟输入的信号调理设计一个标准的处理模块:尺寸为233.35mm×80mm×1槽空间。这样信号线全部在箱体后部接入。每个业务板一一对应预处理的数字信号按照预定的方式通过P5高速传送到对应业务板上的FIFO。FIFO控制器根据触发的有效来变换工作方式。

考虑到系统扩展和故障排除的便利,业务处理板设计成统一的架构。这样,用户针对不同的处理业务只要更改设计好的软件内核,硬件接口程序和用户界面都不用更改。同样,排除故障时只要更换问样的业务板即可完成。

业务处理板尺寸为233.35mm×160mm×1槽空间;支持PICMG 2.1热插拔规范。

板上DSP和FPGA各自带有RAM,用于存放业务处理过程所需要的数据。

APP下载

APP下载 登录

登录

热门文章

热门文章