1. E5的特点及体系结构

E5是位于美国硅谷的公司Triscend 推出的一款全新的CPU,它是基于8051的内核,但将微处理器的内核,ASCI及可重构逻辑阵列集成与一体,构成一款CSOC(可配置系统)芯片。Triscend E5的主要特点有:

1.1 它的主控制器是一个增强型的8032,与工业标准的8051指令上完全兼容。

1.2 它包含一个嵌入式的可重构系统逻辑矩阵(CSL)。共有2048 个可配置系统逻辑(CSL)单元(约40000 个逻辑门)。

1.3 拥有一个高性能的系统总线(CSI),连接微处理器,存储器和可重构系统逻辑矩阵。

1.4 增加了一个存储器接口单元(MIU),负责连接外部存储器。

1.5 片上64k 字节的系统专用RAM(XDATA RAM)

由此可知,E5的主要部件是:8032增强型CPU,可重构系统逻辑矩阵(CSL),内部系统总线(CSI),片上64KRAM,可编程I/O口以及一些专用外设。

2. E5存储区的映射关系

E5内部含有64K的SRAM供数据存取之用,但不含ROM。因此须接以External Memory供程序运行。在使用E5的系统中,E5可以从Internal RAM或External Memory中取得指令运行。一般情况下,E5从External Memory中取得运行指令,而External Memory一般为FLASH。

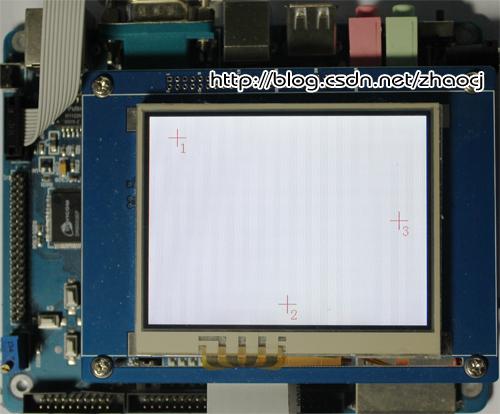

E5使用增强型的8051内核,其逻辑寻址能力遵循8051的规则,即逻辑地址上CODE、XDATA区各64KByte。在传统的8051系统中,指针DPTR可利用指令MOVC、MOVX分别寻址CODE、XDATA的64KByte。但E5利用其MIU(Memory Interface Unit)将实际物理寻址范围作了极大的提升。在使用E5的系统中,合理利用TRISCEND提供的地址映射器CMAP、DMAP,使得寻址范围达到32位的物理地址空间。图1为逻辑地址空间与物理地址空间的映射关系。

从图中可知E5的物理地址划分如下:

0000_0000~0000_FFFF Primary Initialization Code ROM(初始化代码ROM空间)

0001_0000~0001_FFFF Internal RAM(内部RAM空间)

0002_0000~0002_FFFF Configuration Register Unit(可配制寄存器单元)

0003_0000~0003_FFFF CPU Debug Registers(CPU仿真寄存器)

0004_0000~0007_FFFF Initialization Memory(初始化存储器空间)

0008_0000~0009_FFFF Reserved(保留空间)

0010_0000~007F_FFFF CSL-based Soft Module Registers Decoded via Selectors(软件IP库寄存器空间)

0080_0000~00FF_FFFF External Memory(外部存储器空间)

下面再分析实际使用中FLASH MEMORY的空间分配问题。

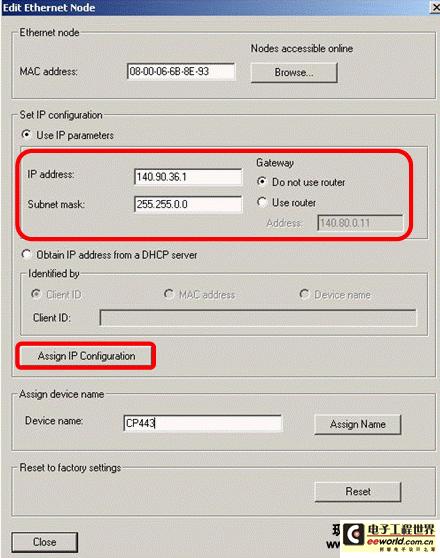

在本文利用E5所设计的应用系统中,使用29LV800BA-90PFTN,作为External Memory程序存储器。它的容量是8M (1M * 8/512K * 16)BIT,并以64K分段(SECTORED)。它的段(SECTOR)空间与E5的物理地址的对应关系如图2所示。

APP下载

APP下载 登录

登录

热门文章

热门文章