在通信系统中分析计算系统抗噪声性能时,经常假定信道噪声为加性高斯型白噪声(AGWN)。本文就是通过分析AGWN的性质,采用自顶向下的设计思路,将AGWN信号分成若干模块,最终使用Verilog硬件描述语言,完成了通信系统中AGWN信号发生电路的设计和仿真,其实质上是设计一个AGWN信号发生器。该信号主要应用在数字通信系统中,所以只需要产生数字形式的AGWN信号,这样既便于信号产生,也便于在数字通信系统中运用。

1 AGWN信号的产生

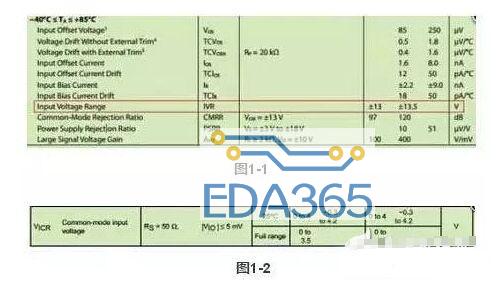

AWGN信号指同时满足白噪声和高斯噪声的条件的信号。白噪声功率密度函数在整个频率域内是常数,即服从均匀分布。完全理想的白噪声不存在。高斯噪声指概率密度函数服从高斯分布(即正态分布)。AGWN信号其实就是一个具有确定功率谱密度和概率分布函数的随机信号。

由随机过程的理论可以知道,不相关随机序列的功率谱密度为常数(白噪声),伪随机序列(PN)就是这样的不相关序列。再由中心极限定理,独立同分布的随机变量的和收敛于高斯随机变量。这样就可根据PN序列的性质和中心极限定理来设计AWGN信号。

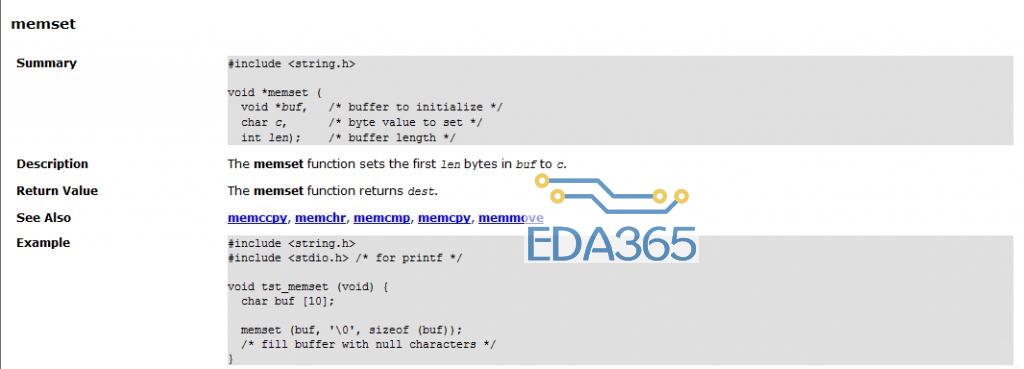

为简单起见,设计用8个PN序列发生器产生8个独立的伪随机序列(每个分为实部和虚部),根据中心极限定理,将8个信号相加之后的信号,更加接近于AG-WN信号,最后再乘以一个可变系数,就产生了可在数字通信系统中直接引用的AGWN信号。AGWN信号生成的总体框图如图1所示。

在FPGA内部产生n位并行伪随机序列,可由n个并行的结构相同但初始态互不相同的线性反馈移位寄存器(LFSR)产生。结构相同的LFSR在不同初始状态下产生的序列之间存在着一种移位关系,导致n个序列并非相互独立。如果所期望的序列长度为k,那么只有在保证任一状态在k次移位操作之内都不会与其他状态发生重复后,这种方法才是可取的。

在通信中,信号一般都表示为复数形式,所以该设计采用了实部与虚部的表示方法,AGWN信号分为实部与虚部,它们满足正交关系。

2 模块的设计与实现

设计主要分为三大模块:PN序列产生模块,产生符合高斯型白噪声伪随机序列;加法器模块,将产生的8个PN序列相加产生更加符合AGWN信号的伪随机序列;乘法器模块,将加法器产生的伪随机序列乘以一个可变系数,得到最终的符合数字信号的伪随机序列。

2.1 n个PN序列发生器的设计与实现

PN序列产生模块的主要功能就是产生PN序列。而PN序列中m序列又是周期最大,伪随机性最好的一种移位寄存器序列。m序列的自相关性、随机性特性很好地满足了AGWN信号的要求,故用其产生的序列可以来产生该设计中的信号。

要产生m序列,就要求移位寄存器的反馈链路满足本原多项式,由,n个并行的结构相同但初始态互不相同的线性反馈移位寄存器(LFSR)产生的序列在其周期足够长的情况下可以把它们看作是独立的。

设计中选取n=8,移位寄存器位数选取为25位,其m序列周期为33 554 431。其信号实部抽头选取3,0,虚部抽头选取3,2,1,0,分别对应PN序列的特征多项式。这样选取是因为一个移位寄存器的本原多项式有很多种,这里选取的两个抽头比较简单,对电路实现在资源、结构上都有优势。PN发生器选择8个是考虑到资源利用率方面的问题,这样选取可使资源利用率达到最大。

2.2 叠加电路设计与实现

根据中心极限定理,对于若干个独立同分布的随机变量,其和的极限分布是标准正态分布。这样将产生的8个序列叠加将产生符合高斯特性的序列。发生器串行输出的实部,虚部8个独立的码相异或。即每8个一位二进制数相异或。

APP下载

APP下载 登录

登录

热门文章

热门文章