摘要: 针对某型现代军用飞机的研制要求,设计了基于ARM 微处理器的机载语音告警系统。该系统硬件设计采用立体数字语音转换器,并对语音采用差分方式输出以提高抗干扰能力,设计了50 ms 掉电保护。软件采用U-Boot 的移植及告警命令优先级的调度处理技术,并将大语音库从NAND Flash 直接加载到SDRAM 中,减小发音间隔。其应用结果表明,该机载语音告警系统能根据战场形势变化解析告警命令后对飞行员发出告警语音,并且接收到告警命令到发出告警语音间隔小于40 ms,适应现代复杂多变的战场环境,告警语音音质清晰、无间断音。

飞机语音告警系统是新型飞机必备的一种机载设备,其作用是将飞机当前的工作状态、危险状况或者通过数据链获取的作战任务命令,实时以语音方式告知飞行员[1]。在飞机飞行过程中飞行员一般是通过安装在座舱里的操作台、仪表和告警信号灯来了解飞机各个系统的工作状态。由于飞行员在飞行时为完成相应的飞行任务, 注意力高度集中在飞行高度、速度和雷达参数等数据信息上,对飞机故障信息的注意力要相对弱一些,这样就会出现飞行员不能及时地对故障采取措施,从而导致严重的飞行事故。同时,目前大多数新研制或改装的飞机都有数据链系统,许多作战任务命令不再单纯依靠地面指挥人员或长机的语音传达,可通过数据链或根据战场态势产生,并及时告知飞行员,因此,针对某新型飞机的研制要求,设计了基于ARM 单片机的语音告警系统。

1 系统总体框架设计与工作原理:

语音告警系统由以下6 部分组成: 语音命令输入单元、语音命令真伪和优先权判断单元、告警语音播放单元、电源及其监控单元、自检测单元和调试接口,系统设计框图如图1 所示。

系统的语音告警数据可以通过JTAG 预先装载到非遗失的NAND Flash 中, 系统上电后自动将告警软件和语音告警数据加载到SDRAM 中。系统工作时,通过RS422 接收外系统传来的一个或多个告警命令,按照告警命令的优先级依次发出告警语音。当新的告警命令优先级高于当前告警命令时,中断当前告警语音;当高优先级的告警命令处理结束后,接着依次发出较低一级的告警语音。

2 硬件设计:

2.1 ARM 处理器单元:

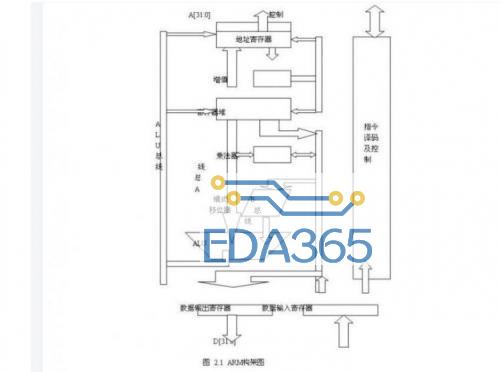

ARM 处理器单元由S3C2440 型ARM、存储单元的NAND Flash 和SDRAM 组成。

2.1.1 S3C2440 寻址原理:

S3C2440是基于ARM920T 内核的16/32 位RISC 微处理器[2],提供32 位地址总线,可以访问4 Gb 的线性地址空间,而S3C2440 的内部地址总线是30 b,能够访问的最大外部地址空间是1 GB, 可见S3C2440 仅利用ARM920T 32 位地址空间的低30 位。S3C2440 将1 GB 的外部地址空间分成了8 个存储器组, 每个组的大小128 MB, 其中6 个用于ROM、SRAM 等存储器,2 个用于ROM、SRAM、SDRAM 存储器。S3C2440 对外寻址时,采用了部分译码的方式,低位地址线用于外围存储器的片内寻址, 高位地址线用于外围存储器的片外寻址。高3 位ADDR[29:27]来选择该地址属于哪一个存储器组,ADDR [26:0]来实现相应存储器组的内部寻址,寻址范围为128 MB,从而使得其外围地址访问空间为1 GB。

2.1.2 存储单元设计:

NAND Flash 接口信号较少(如图2 所示),数据宽度只有8 b,没有地址总线,地址、数据总线复用, 串行读取, 以页(page)为单位进行读写,以块(block)为单位进行擦除。操作NAND Flash 时,先传输命令,然后再传输地址,最后读写数据。本系统采用64 M×8 bit 的K9F1208,其组织方式可以分4类地址:

1)Column Address 表示数据在半页中的地址, 大小范围0~255,用A[0:7]表示;2)Halfpage Pointer 表示半页在整页中的位置, 即在0~255 空间或256~511 空间,用A[8]表示;A[8]=00 为上半页,A[8]=01 为下半页;3)Page Address 表示页在块中的地址, 大小范围0~31,用A[9:13]表示;4)Block Address 表示块在Flash 中的位置,大小范围0~4 095,A[14:25]表示。

对NAND Flash 操作时,地址分4 个周期传送。

APP下载

APP下载 登录

登录

热门文章

热门文章