摘 要: 在分析光电跟踪伺服系统特点的基础上,以TI公司DSP芯片TMS320F2812作为主控制芯片,采用FPGA进行逻辑时序控制,设计了基于DSP和FPGA的多轴伺服运动控制器。给出了该控制器的功能和硬件结构以及软件流程设计。实验结果表明,该控制器具有高集成度、灵活性、实时性、模块化的特点,完全满足了在复杂环境下对伺服系统控制的要求。

在高速光电跟踪系统中,对伺服系统的高速性、精确度和稳定性都有很高的要求。为了提高跟踪精度,越来越多的控制算法被应用于伺服系统中,因此要求控制器能在很短的时间内完成大量的运算[1]。DSP具有较强的运算能力,而FPGA具有高度灵活的可配置性和逻辑时序控制能力[2]。因此在很多伺服控制器中,“DSP+FPGA”结构得到了广泛的应用。

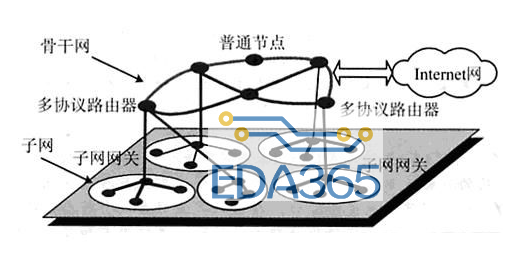

实际应用环境一般比较复杂,有大量的信息传递,并且需要对电机转速实行精确控制,因此对伺服控制器的多路通信能力,快速运算能力和抗干扰能力都有较高的要求。为了解决这一问题,提供一个较好的实验平台,本文结合光电跟踪伺服系统的特点,提出一种以TI公司的32位定点数字信号处理器TMS320F2812为核心,以Altera公司CycloneⅡ系列FPGA为辅助处理器结构的跟踪伺服控制器,并综合阐述了该控制器的功能、硬件设计和软件流程。该控制器采用单+5 V供电,具有6路模拟信号输入、4路模拟信号输出、多路PWM输出、1路CAN总线、2路RS422和1路RS232串行通信口,具有较强的运算能力和数据通信能力,是良好的数字控制系统实验平台。

1 总体结构设计

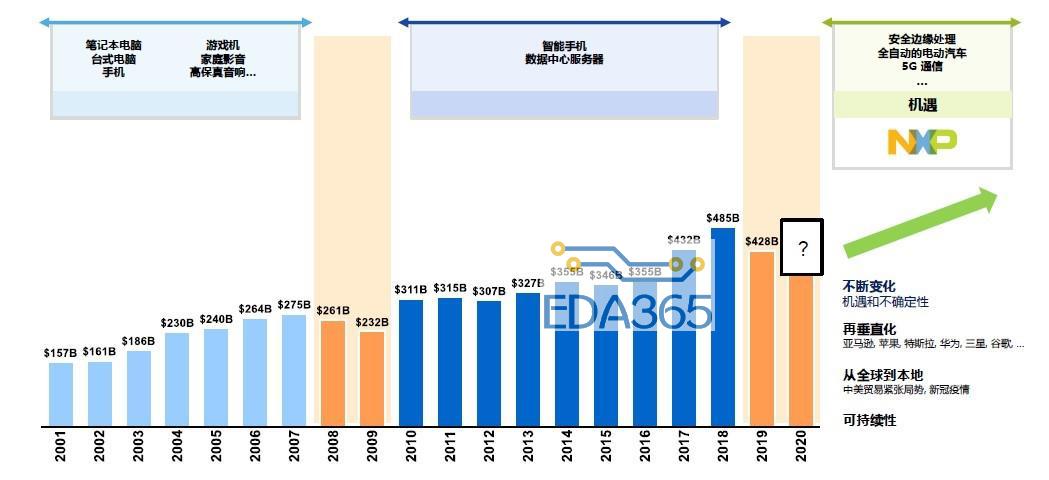

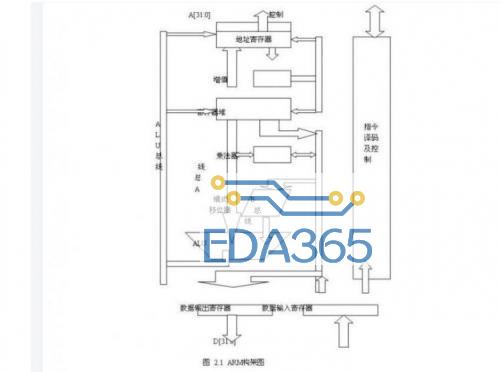

TMS320F2812作为一款专为电机控制所设计的芯片,不仅具有运算速度快的特点,而且集成了丰富的片内外设资源[3]。设计时综合考虑DSP片上资源的充分利用、系统的模块化和可移植性等特点,将整个控制器大体分为4个部分:DSP模块、FPGA模块、D/A转换模块和通信接口模块。控制器的总体硬件结构如图1所示。

从图1中可以看出,DSP通过CAN总线接收上位机指令;位置信号通过两路RS422通信口传给DSP作相应处理;速度信号是由DSP片上集成的QEP电路对电机产生的正交编码脉冲信号进行解码获得;DSP输出的PWM信号与FPGA相连,通过FPGA内部的保护模块后经光电隔离输出到功率放大模块。外部中断经FPGA片内中断控制逻辑后输出到DSP外部中断管脚上;DSP与FPGA之间的数据交换通过DSP片上的多通道缓冲串口(Mcbsp)来实现;D/A转换器控制由FPGA内部的D/A转换接口模块接收DSP传来的数字量并控制逻辑时序;计算机调试接口采用RS232。

2 硬件电路设计

2.1 DSP模块

32位定点数字信号处理器TMS320F2812整合了DSP和微控制器的最佳性能,能够在一个周期内完成32×32 bit的乘法运算,或2个16×16 bit乘法累加运算,处理速度最高可达150 MIPS。它采用高性能静态CMOS技术,内核电压为1.8 V@135 MHz,1.9 V@150 MHz, I/O端口电压3.3 V[4,5]。其先进的内部和外设结构使得该处理器特别适合电机及其他运动控制应用,能够真正实现单片控制,为电机的伺服控制提供了良好的控制功能[6]。

DSP的功能主要通过软件实现,在此主要实现接收上位机指令,完成位置环和速度环反馈的双闭环控制算法,以及速度的PID调节,产生PWM输出。由于实际工作环境较为复杂,所以选用了抗干扰能力强的CAN总线作为与上位机的通信方式,TMS320F2812内部集成了一个eCAN模块,只需增加相应的CAN收发器外围电路就可以实现通信。根据系统采样频率调整事件管理器的定时器,控制寄存器的控制字来设定PWM工作方式和频率,通过调整比较寄存器的数值来改变PWM的占空比,根据功率驱动电路的驱动芯片来设置死区控制寄存器的数值来调整死区时间,通过专用的PWM输出口输出占空比可调的带有死区的PWM信号[7]。

APP下载

APP下载 登录

登录

热门文章

热门文章