在现代通信、雷达和声纳系统中,随着实时处理要求的不断提高,对数字信号处理系统也提出了更高的要求。板载多片高性能的DSP芯片,配合大容量的SDRAM,可以很好地满足上述要求,并且已经成为了数字信号处理系统发展的趋势。采用CPCI总线集成系统,可以方便主机进行调试,控制和管理DSP系统。系统中的主机接口可以使主机通过CPCI总线访问板上的DSP和SDRAM芯片,这是多DSP系统设计的关键点之一。

不同于以往简单地使用一个CPLD进行粘合逻辑设计,本文提出了一种基于双状态机+Cache,预存预取的主机接口设计结构。在主机接口中设立了一个Cache,降低了CPCI总线与板上DSP和SDRAM芯片的耦合度,并且设计了两个独立状态机分别进行控制。这显著提高了主机访问DSP和SDRAM的速度,为DSP系统的应用提供了更广阔的平台。本文详细阐述了如何完成CPCI总线和DSP、SDRAM芯片间的数据传输,分析了设计难点,并给出了逻辑框图。

1 系统设计方案

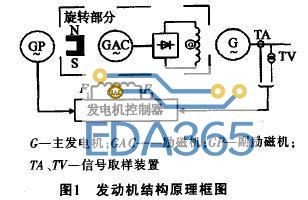

图1是系统设计框

图,系统采用PLX公司的PCI9656接口芯片,它可以很方便地将时序相对复杂的PCI协议转化为相对简单的局部端访问协议。在基本不损失性能的同时,简化了逻辑设计要求,使开发者可以更为关注后端数据接口问题。

FPGA采用Xilinx公司的X2V1000它有近100万门的逻辑资源和720KB的BlockRAM可以灵活搭建控制逻辑和Cache缓存DSP采用ADI公司的… src=Image/20090601155734566221_new.jpg>

FPGA采用Xilinx公司的X2V1000,它有近100万门的逻辑资源和720KB的BlockRAM,可以灵活搭建控制逻辑和Cache缓存。

DSP采用ADI公司的ADSP-TS201S,共有4片,工作频率是600MHz,总共可以提供14.4GFLOPS的运算能力[1]。

SDRAM采用Hynix公司的HY57V561620C,容量共有128MB,可以基本满足数据存储的要求。

2 FPGA的接口设计

2.1 FPGA在系统中的作用

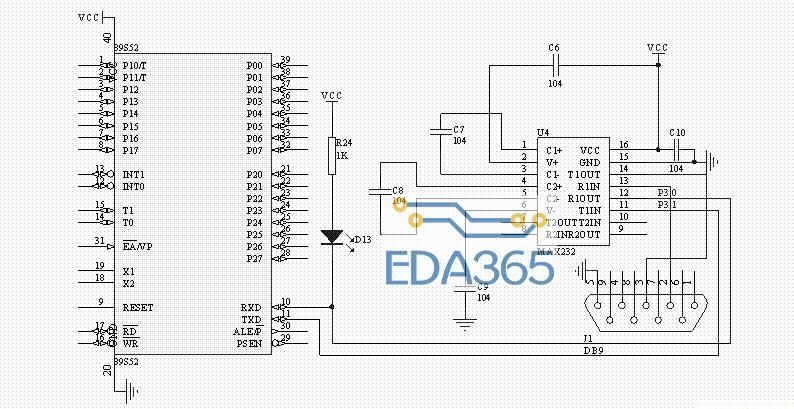

FPGA主要实现如下功能接口:(1)DSP接口。提供一个PCI Local总线到DSP共享总线的界面,完成两套总线之间的逻辑仲裁及读写控制信号等;(2)SDRAM接口。提供一个PCI Local总线到SDRAM总线的界面;(3)FLASH接口;(4)链路口;(5)Register管理模块。图2给出了FPGA的各种接口与系统其他部分的关系图。本文将重点讨论主机和DSP、SDRAM间的访问。

APP下载

APP下载 登录

登录

热门文章

热门文章