0 引言

近些年信息通信领域中发展最快、应用最广的就是无线通信技术。而无线通信技术又有着集成化、低功耗、易操作的发展趋势。微功率短距离无线数据传输技术作为一种无线通信实用技术,一般使用单片射频收发芯片,加上微控制器和少量外围器件构成专用或通用无线通信模块,只要依据命令字进行操作即可实现基本的数据无线短距离抄表功能。本文提出了一种基于CCll00的无线自动抄表系统,其通信质量好、成本低、工作可靠、经济实用,可以准确及时地将用户三表数据抄送上来, 是一种理想的自动抄表解决方案, 同时也是抄表收费系统发展的趋势。

1 抄表系统结构

抄表系统主要由主站、GPRS通信信道、集中器、低压电力线网络、数据采集器、用户电表组成。系统工作原理是利用低压电力线或者RS一232总线将电表数据由采集器传输到集中器,然后集中器将信号定时或实时地传送至GPRS网络,经网关支持节点(Gateway GPRS Support Node,GGSN)完成与Internet网络的数据交换,最后由主站的计算机接收Internet上的数据并进行用户电表数据汇总、电费计量、线损分析等相关处理。

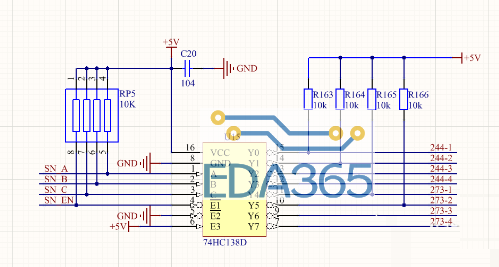

系统可用于家庭内部三表或多表数据的抄送。系统下层直接与水表、电表、煤气表等连接,上层与抄表中心主机连接,实现数据的远程抄送。系统一般使用被动抄表方式。上层模块接收到仪表中心的抄表命令时,通过无线方式向下层模块发送抄表指令。无线抄表系统的总体框架如图l所示。

2 主要器件的介绍

2.1 AT89S52的主要特点

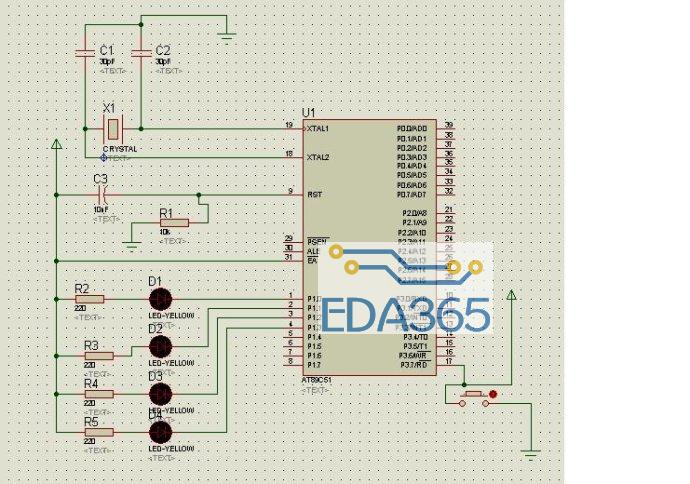

A89S52是一种低功耗、高性能CMOS8位微控制器,具有8k在系统可编程F1ash存储器。片上F1ash允许程序存储器在系统可编程,亦适于常规编程器。在单芯片上,拥有灵巧的8位CPU和在系统可编程Flash,使得AT89S52为众多嵌入式控制应用系统提供了高灵活、超有效的解决方案。

A89S52与MCS一5 l单片机产品兼容,具有8k字节在系统可编程F1ash存储器、1000次擦写周期、全静态操作:OHz~33Hz、三级加密程序存储器、32个可编程I/O口线、三个16位定时器/计数器、八个中断源、全双工UART串行通道、低功耗空闲和掉电模式、掉电后中断可唤醒、看门狗定时器、双数据指针、掉电标识符。

2.2 CCll00主要性能

CCll00是一种低成本真正单片的UHF收发器,为低功耗无线应用而设计。电路主要设定为在315、433、868和915MHz的ISM(工业,科学和医学)和ISRD(短距离设备)频率波段,也可以容易地设置为300~348MHz、400~464MHz和800~928MHz的其他频段。RF收发器集成了一个高度可配置的调制解调器。其数据传输速率可达500kbps。通过开启集成在调制解调器上的前向误差校正选项,能使性能得到提升。CCll00为数据包处理、数据缓冲、突发数据传输、清晰信道评估、连接质量指示和电磁波激发提供广泛的硬件支持。CCll00的主要操作参数和164位传输/接收FIF0(先进先出堆栈)可通过SPI接口控制。

3 硬件设计

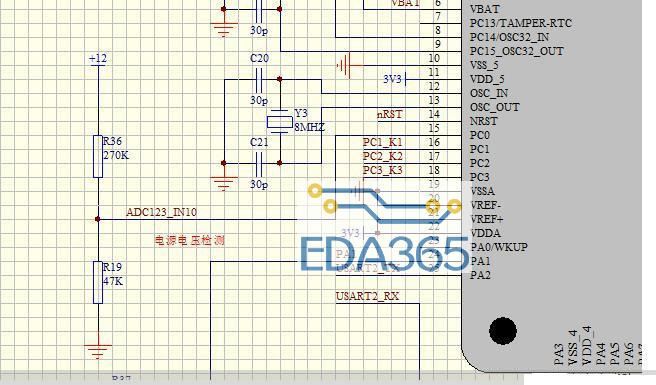

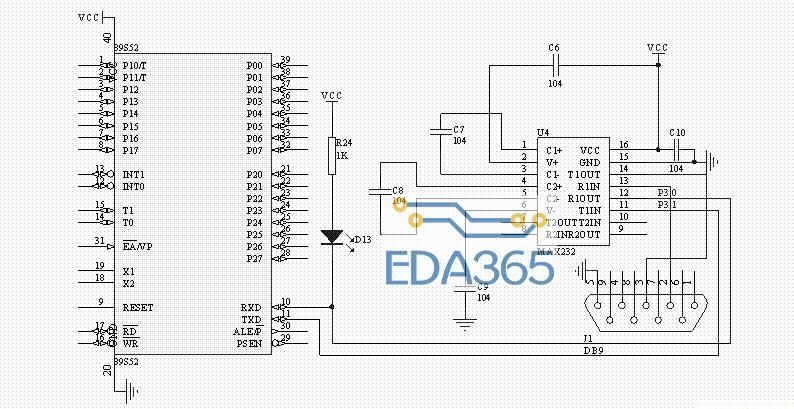

单片机对发射模块和接收模块的控制,首先都要对单片机的接口进行初始化(SPI总线接口技术是一种高速、高效率的串行接口技术,主要用于扩展外设和进行数据交换。),然后要对射频模块初始化,在这部分的初始化中要上电复位芯片和对它的片内寄存器进行配置。发射端发射一组数据中首先要通过口对,缓冲区设置单次发送的数据个数,然后写入要发送的数据包,数据自动加前导码和校验,接着进入发送模式发送数据包,等待本次发送结束,最后冲洗缓冲区,本次发送完毕。接收端接收一组数据中首先进入接收模式,等待接收信息完成,然后接收到的数据包被分解,读出所有接收到的数据并存储,最后清洗缓冲区,本次接收完毕。CCll00具有包处理机制、发送、接收FIF0、WOR模式(Wake on Radio)等诸多特点。在CCll00之前的无线收发芯片都是采用同步方式将数据按位发送出去,这种方式在发送与接收数据时处理起来比较麻烦,接收时还要判断前导字与同步字。而CCll00把这些繁琐的工作承担下来,当需要发射数据时,只需将发射的数据按照一定的格式通过SPI口写入到发射FIF0,然后把CCll00配置成发射状态,数据就会按照要求发射出去;当需要接收数据时,首先将CCll00配置成接收状态,一旦收到符合要求的数据,CCll00就会把收到的数据存入接收FIF0,同时引脚GD00或GD02会有一个脉冲出现,这个脉冲可以用来通知MCU有一个数据包已被CCll00收到,MCU就可以通过SPI口将CCll00收到的数据取出来。硬件连接如图2所示。

APP下载

APP下载 登录

登录

热门文章

热门文章