1 内存条的工作原理

DDR内存条是由多颗粒的DDR SDKAM芯片互连组成,DDR SDRAM是双数据率同步动态随机存储器的缩写。DDR SDRAM采用双数据速率接口,也就是在时钟的正沿或负沿都需要对数据进行采样。在本设计中采用的内存是hynix公司的lGB的HYMD564M646CP6-J。内存条的工作原理与单颗粒内存芯片的工作原理一样,主要的控制信号以及控制信号完成的主要功能如表1所示。

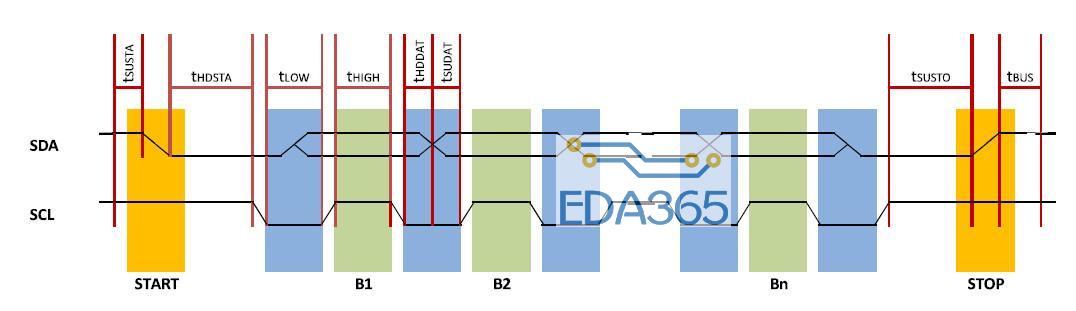

以上的控制信号及地址信号都是由差分时钟信号中CK的正沿触发。DDR SDRAM必须按照一定的工作模式来完成初始化,完成初始化后才能进入到读写过程。DDR SDRAM的控制流程如图1所示。

初始化的过程为:(1)上电后,延时200us等待时钟稳定,然后将CKE拉高,执行一次NOP或者DESELECT操作。(2)执行一次precharge all操作。(3)设置扩展模式寄存器(BAl为低电平BA0为高电平)使能DLL。(4)设置模式寄存器(BAl,BA0均为低电平)复位DLL。(5)执行一次pre-charge all指令。(6)再经过2个自刷新(Auto refresh)指令后再次设置模式寄存器设置操作模式。(7)延时200个周期才能进行读操作。DDR SDRAM的扩展模式寄存器和模式寄存器的定义如图2和图3所示。

完成初始化后进入图1中的IDEL状态,此时可以进行读写操作。在进行写操作时,首先要进入Row active状态,此时选中要操作的bank与row。然后执行NOP操作等待tRCD的时间后可以进入写状态。

APP下载

APP下载 登录

登录

热门文章

热门文章