我们将针对FPGA中内部BlockRAM有限的缺点,提出了将FPGA与外部SRAM相结合来改进设计的方法,并给出了部分VHDL程序。

2 硬件设计

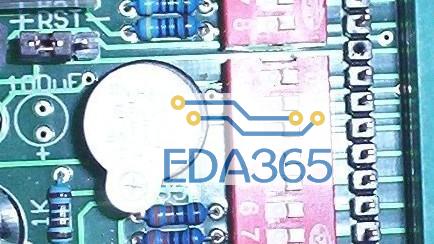

这里将主要讨论以Xilinx公司的FPGA(XC2S600E-6fg456)和ISSI公司的SRAM(IS61LV25616AL)为主要器件来完成大容量数据存储的设计思路。

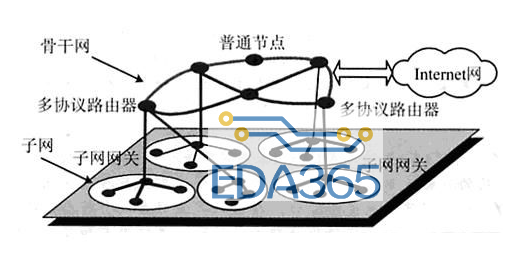

FPGA即现场可编程门阵列,其结构与传统的门阵列相似,大量的可编程逻辑块( CLB , Configurable Logic Block ) 在芯片中央按矩阵排列,芯片四周为可编程输入/输出块( IOB , Input / Output Block),CLB行列之间及CLB和IOB之间具有可编程的互连资源(ICR,InterConnectResource)。CLB、IOB和ICR都由分布在芯片中的SRAM静态存储单元控制,SRAM中的数据决定FPGA的功能,这些数据可以在系统加电时自动或由命令控制从外部存储器装入。

在进行数据存储时,可直接将数据写入FPGA内部的BlockRAM中,在一定程度上减少了FPGA的资源分配。但FPGA内部自带的RAM块毕竟是有限的,当需进行大容量数据存储时这有限的RAM块是远远不能满足系统设计要求的。此时,就需要将FPGA与外部RAM相结合完成大容量数据存储。具体硬件电路如图一所示:

3 IS61LV25616AL功能简介

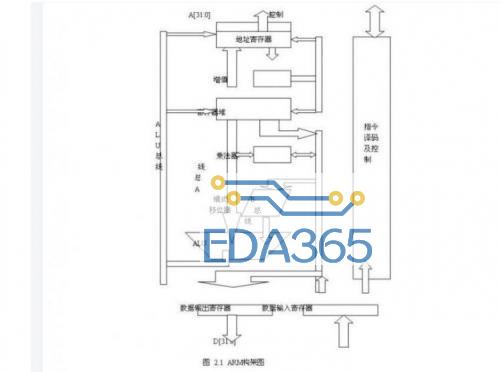

IS61LV25616AL是Integrated Silicon Solution公司(ISSI)的一款容量为256K×16的且引脚功能完全兼容的4Mb的异步SRAM,可为Xilinx公司的Spartan-2E系列FPGA提供高性能、高消费比的外围存储。除了256K×16异步SRAM外,ISSI还提供128K×16、512K×16、256K×8、512K×8和1M×8的异步SRAM。 IS61LV25616AL引脚结构框图如图二所示:

3.1 主要特征

(1)工作电压:3.3伏;

(2)访问时间:10ns、12ns;

(3)芯片容量:256K×16;

(4)封装形式:44引脚TSOPII封装,也有48引脚mBGA和44引脚SOJ封装;

(5)采用0.18μm技术制造。

3.2 引脚功能

(1)A0~A17:18位的地址输入线;

(2)IO0~IO15:16位的三态数据输入输出线;

(3)写控制线;

(4)片选信号;

(5)输出使能信号;

(6)低字节、高字节使能信号;

(3)~(6)的控制线均为低电平有效。

APP下载

APP下载 登录

登录

热门文章

热门文章