摘要:鉴于目前常用的基于计算机的并行频域OCT图像预处理系统速度慢、体积庞大等缺陷,设计了基于ADSP-BF561的图像处理硬件平台。该平台包括了ADSP-BF561最小系统、视频采集解码电路、视频编码显示电路等部分。实验表明:该平台提高了图像处理速度,并且实现了系统的小型化。

关键词:并行频域OCT;ADSP-BF561;硬件平台

*国家自然科学基金项目(项目编号60674111)

2008年7月3日收到本文修改稿。李刚:教授,从事信号检测与处理、智能仪器仪表的研究。

引言

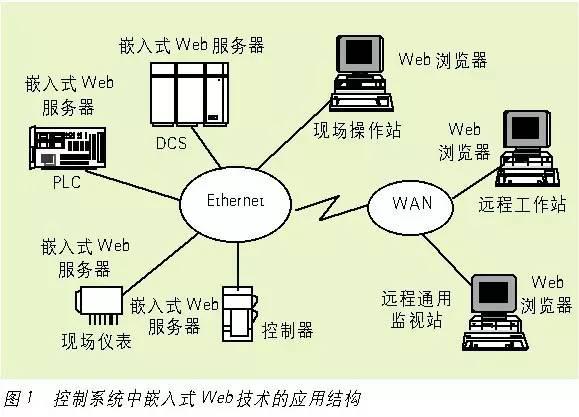

光学相干层析成像(OCT)是一种迅速发展的无损伤、高分辨率医学层析成像技术[1-2]。新近发展起来的并行频域OCT(PSDOCT)无需轴向和横向扫描即可得到样品一行深度信息的层析图像,已成为实时OCT成像发展的趋势[3-4]。并行频域OCT图像预处理系统结构如图1所示,系统由光学系统和图像处理系统两部分组成,原理如下:从宽带光源发出的光经分光棱镜分束后分别照射到样品和参考镜(反射镜)上。柱面镜1将其子午面M内样品反射回来的光聚焦为平行于柱面镜母线的一条直线,与参考镜反射回来的参考光发生干涉,经光栅分光及柱面镜2聚焦后通过图像采集电路进行图像采集。由于样品反射回来的光信号被样品的反射系数所调制,通过图像处理系统对输出的频域图像进行逐行IFFT(快速傅里叶逆变换)、幅度谱计算并进行直流项移位即可得到位于柱面镜1子午面内样品的二维层析图像。并输出在显示器上显示。

图1 并行频域OCT图像预处理系统

目前大多数OCT图像处理系统由摄像机、图像采集卡及计算机组成。用摄像机和图像采集卡完成图像采集功能,图像处理则是由软件在计算机中完成[5-6]。由于计算机体积庞大,并且是任务分时处理系统,运行过程中的其他任务可能影响OCT成像的速度,而且下位机与计算机之间的通讯速度慢,所以目前还无法满足并行频域OCT成像系统便携化、快速处理的需求。鉴于此,本文设计了以ADI公司双核定点DSP — ADSP-BF561[7-8]为核心,结合视频解码和编码技术的并行频域OCT图像预处理系统硬件平台。

ADSP-BF561

ADSP-BF561(下面简称BF561)是ADI公司和Intel 公司合作推出的基于微信号体系结构技术的定点DSP,整合了传统体系结构DSP和RISC控制器的优点。该器件采用改进的哈佛结构以及多级流水线结构。其核心由两枚独立且对称的600 MHz高性能Blackfin处理器组成。

硬件设计

本方案利用BF561的特点,设计出并行频域OCT图像预处理系统的硬件平台(见图2)。该平台包括了ADSP-BF561最小系统、视频采集解码电路、视频编码显示电路等部分。

图2 系统硬件结构

ADSP-BF561最小系统

ADSP-BF561最小系统由ADSP-BF561、电源电路、时钟电路、复位电路、JTAG接口电路、SDRAM、FLASH等部分组成。

·供电电源

系统为三电压供电,包括:1.2V的内核电压,3.3V的I/O电压和ADV7183的电压,3V的ADV7179电压。采用TPS75003 DC-DC控制器实现分别提供1.2V、3.3V 、3V电源供应。

·系统时钟

BF561时钟信号既可以由内部放大器与外接晶体或陶瓷谐振器构成的振荡器提供,也可以直接采用外部时钟输入。

·复位电路

系统复位电路采用简单的RC充、放电电路。

·JTAG接口电路

BF561提供了一个IEEE 1149.1 J TAG 测试访问接口。通过此接口可以实现在线仿真、程序下载等操作,并且可以设置断点,观察变量和寄存器,系统采用14针接口的标准。

·SDRAM电路

由于视频数据信息量很大,而ADSP-BF561内部存储器容量有限,所以系统需要外扩SDRAM作为视频数据的缓存器。BF561具有的兼容PC133的SDRAM控制器可以通过编程与多达4个BANK的SDRAM连接,每个BANK的容量最多可达128MB。本系统选用两片16位32MB容量的SDRAM—HY57V561620扩展为一片32位的64MB容量SDRAM,用以灵活实现系统16位或32位的数据读写要求。将其接在BF561同步存储空间的BANK0上,地址范围为0x00000000~0x4000000。BF561与SDRAM的硬件连接如图3所示。

图3 BF561与SDRAM的接口电路

APP下载

APP下载 登录

登录

热门文章

热门文章