PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

PCIe计时

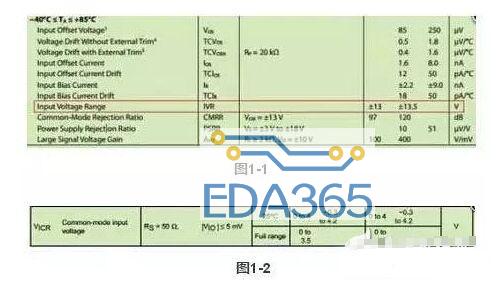

PCIe基本规范1.1和2.0为信令速率2.5Gbps和5.0Gbps的时钟分配定义了三个不同模型,见图1、图2和图3。

PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

PCIe计时

PCIe基本规范1.1和2.0为信令速率2.5Gbps和5.0Gbps的时钟分配定义了三个不同模型,见图1、图2和图3。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多