近日,在2020国际电子器件大会(IEDM)视频会议上,中科院微电子所刘明院士科研团队展示了阻变存储器芯片集成领域的最新研究成果。

阻变存储器(RRAM)因其CMOS工艺兼容性好、微缩能力强、可靠性高等优势,被认为是先进工艺节点上取代e-flash的有力候选者。但其能否集成在10纳米逻辑工艺平台是影响RRAM未来市场的关键因素。

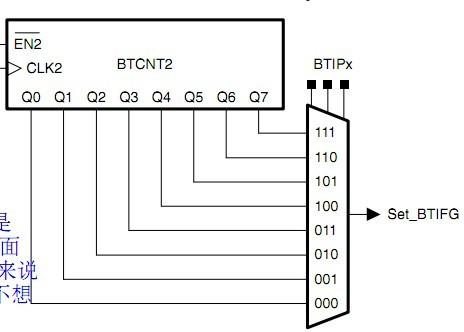

刘明院士团队首次在14纳米 FinFET逻辑工艺平台上开展了RRAM的集成工作,实现了1Mbit的嵌入式RRAM存储芯片,1T1R单元面积为0.022um2,芯片存储密度为13.4Mb/mm2,居世界前列。针对RRAM器件与逻辑单元之间的不兼容性,团队提出了负电压偏置的编程方案,通过在芯片中引入深N阱工艺,使阵列可以施加负电压以降低施加电压的绝对值进而减小传输路径上的高压风险。团队采用位线转置的优化阵列架构,降低了晶体管的击穿风险。团队发现操作电压、编程电流和后端RC是影响微缩的重要因素,进而提出了RRAM在10纳米及以下节点集成的建议设计规则,并采用1T2R的阵列架构提高存储密度。该工作对提升RRAM在先进工艺节点下的嵌入式应用具有一定的指导意义。

基于上述研究成果的论文“First Demonstration of OxRRAM Integration on 14nm FinFet Platform and Scaling Potential Analysis towards Sub-10nm Node”入选2020 IEDM。微电子所许晓欣副研究员为论文第一作者。

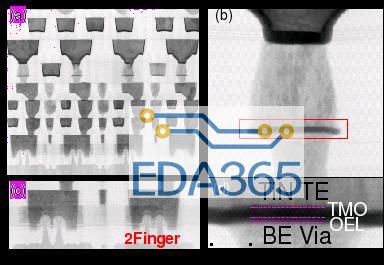

图1 (a)14nm FinFET平台开发的RRAM结构示意图。b)RRAM单元的TEM横截面图像。(c)2Finger 结构的逻辑器件。(d)RRAM的叠层结构

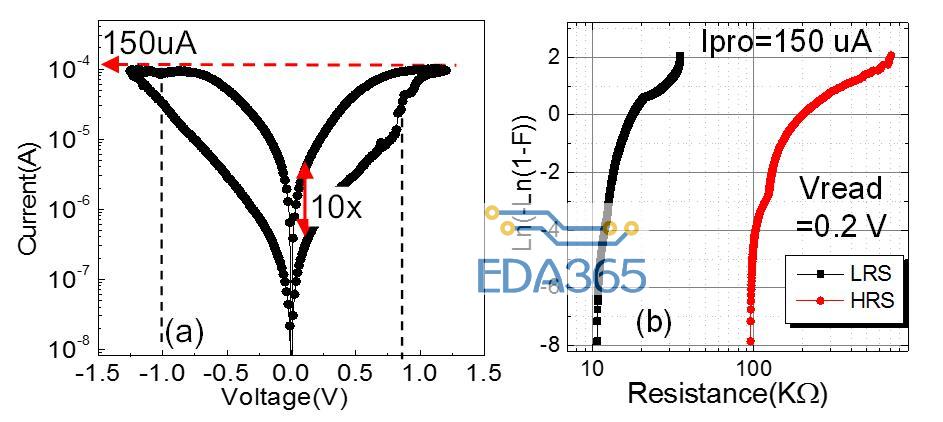

图2 RRAM单元的基本电学特性。(a)IV特性曲线;(b)4Kb存储阵列中高低阻态分布

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多