在深度神经网络(DNN)的简史中,用户已经尝试了几种硬件架构来提高其性能。通用CPU编程最容易,但每瓦特的性能最低。GPU针对并行浮点运算进行了优化,性能比CPU好几倍。随着GPU供应商有了相当大的一批新客户,他们开始改进设计以进一步提高DNN吞吐量。例如,Nvidia新的Volta架构增加了专用的矩阵乘法单元,加速了常见的DNN运算。

即使是增强型的GPU,仍然受其针对图形专用逻辑的拖累。此外,最近的趋势是使用整数运算来进行DNN推理,尽管大多数训练仍然使用浮点计算。Nvidia也增强了Volta的整数性能,但仍然建议使用浮点计算进行推理。但是,芯片设计人员很清楚,整数单元比浮点单元小得多、功效也高得多;当使用8位(或更小)整数而不是16位或32位浮点数时,优势更明显。

与GPU不同,DSP是针对整数数学设计的,并且非常适合于卷积网络(CNN)中的卷积函数。矢量DSP使用宽SIMD单元来进一步加速推理计算。例如,Cadence的C5 DSP内核包括四个SIMD单元、每个2048位宽;这样,内核在每个周期内可以完成1,024个8位整数乘法累加(MAC)操作。在16nm设计中,它能每秒处理超过1万亿个MAC运算。联发科购买了Cadence的DSP IP,用作其最新智能手机处理器的DNN加速器。

最有效的架构是从头开始设计DNN,消除其它应用的特性,并针对DNN需要的特定计算进行优化。这些架构可以用专有的ASIC或向系统制造商销售的芯片(这些芯片被称为专用标准产品或ASSP)来实现。最突出的DNN ASIC是谷歌的TPU,它为推理任务进行了优化。它主要包括65,536个MAC单元的脉动阵列(systolic array)和28MB的内存以容纳DNN体量和累加器。TPU使用一个简单的四级管道,只运行少数指令。

多家初创公司也在为DNN开发自定义架构。英特尔去年收购了其中的一个(Nervana),并计划在今年年底前发布其第一款ASSP样片;但该公司尚未透露其架构的任何细节。Wave Computing已经为DNN开发了一个数据流处理器。其它不差钱的初创公司包括Cerebras、Graphcore和Groq。我们预计这些公司至少有一部分会在2018年交付量产器件。

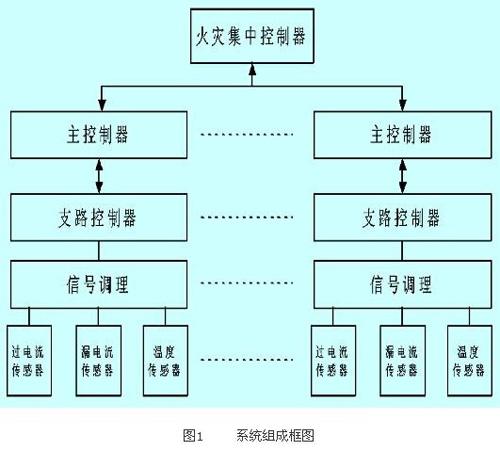

另一种实现优化架构的方法是利用FPGA。微软广泛采用FPGA作为其Catapult和Brainwave计划的一部分;百度、Facebook和其它云服务器提供商(CSP)也使用FPGA来加速DNN。这种方法避免了ASIC和ASSP数百万美元的流片费用,并提供了更快的迭代周期;只要设计有更改,FPGA就可以在几分钟内编程和重新编程。但它们工作在较低时钟速率、并且比ASIC所能容纳的逻辑块少得多。图1总结了我们对这些解决方案的相对效率的看法。

*图:基于不同的硬件设计,深度学习加速器的性能/功耗比至少可以有两个数量级的差异。

*使用自定义架构。 (来源:Linley Group)*

一些公司通过增加一个定制程度更高的加速器来强化现有设计,以对冲他们的风险。Nvidia的Xavier芯片专为自动驾驶汽车设计,增加了一个整数数学模块来加速DNN推理。Ceva和Synopsys设计了类似的单元来增强他们的SIMD DSP内核。这些模块只包含大量的整数MAC单元来提高运算吞吐量。因为它们没替换底层的GPU或DSP架构,所以不像从头设计那样高效。

定制设计面临的一个挑战是深度学习算法正在迅速发展。最流行的DNN开发工具TensorFlow,在两年前还不可用;数据科学家们继续评估新的DNN结构、卷积函数和数据格式。为今天的工作负荷定制的设计、对两年后的DNN来说可能不是理想选择、甚至都不能用。为了解决这个问题,大多数ASIC和ASSP设计是可编程和灵活的,但是FPGA提供了最大灵活性。例如,微软已经将专有的9位浮点格式定义为其Brainwave设计的一部分。

纵观其历史,半导体行业通常首先在通用CPU中实现新应用。如果应用适用于现有的专用芯片,如GPU和DSP,则可能会转移到这两者。随着时间的推移,如果新应用发展成一个规模市场,公司开始开发ASIC和ASSP,虽然这些器件可能保留一定的可编程性。只有当一个算法变得高度稳定时(例如MPEG)才能看到用固定功能逻辑的实现。

深度学习目前也正按这一发展路线展开。GPU和DSP显然是适用的;且因需求足够高、所以ASIC开始出现。几家初创公司和其它公司正在开发将在2018年及以后出货的ASSP。对于小批量或利基应用,FPGA通常更受欢迎;深度学习已经显示出足够的希望来证明该有ASIC问世了。

但是,胜出的DNN架构还远不明朗。尽管深度学习市场正在迅速增长,但仍远低于个人电脑、智能手机和汽车市场。因此,ASIC和ASSP的商业案例尚无足轻重。相比之下,像英特尔和Nvidia这样的公司可以使用其它市场的高性能处理器,并针对深度学习进行强化,通过大量的软件支持和频繁更新来提供具有竞争力的产品。未来几年,我们可能会看到许多不同的硬件架构在深度学习市场中共存。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多