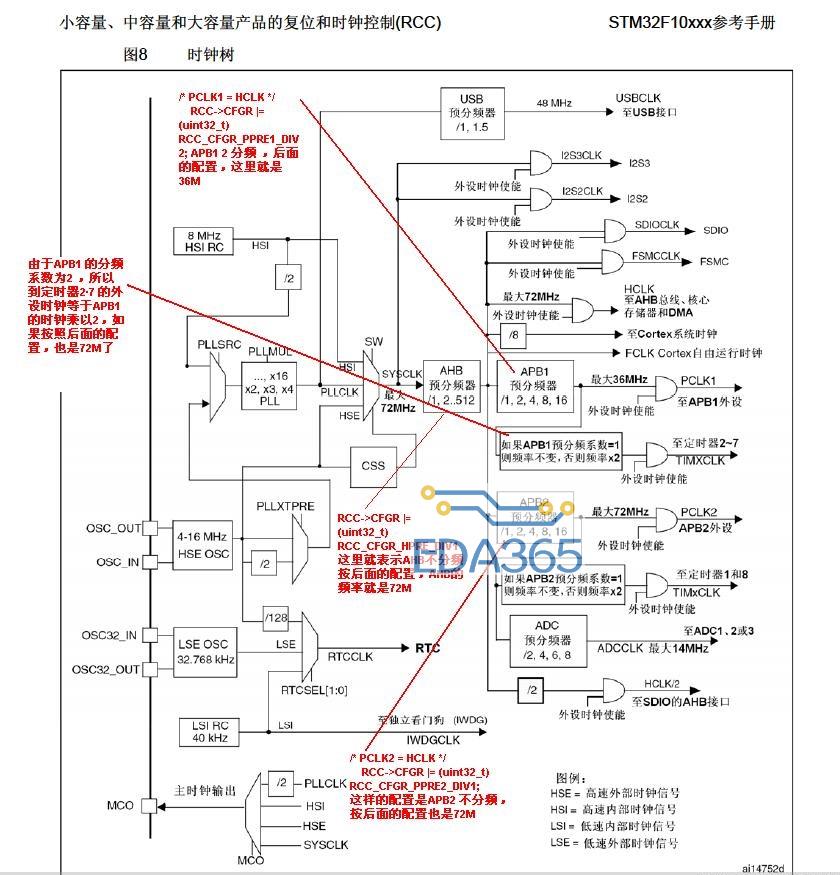

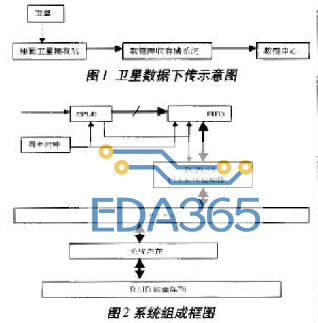

目前卫星技术已广泛应用于国民生产的各个方面。通讯卫星,气象卫星以及遥感卫星,科学探测卫星等与人们的生活密切相关。卫星所收集的大量数据资料能否及时准确地下传、接收和存储是卫星技术的一个重要方面。其传送过程如图 1 所示。

从卫星上高速下传的数据由地面卫星接收站转发为基带信号,通过光缆传送至数据中心,速度可达上百兆波特率,要求系统正确接收,经过同步和预处理,然后存入计算机系统,供数据中心使用。其特点是:数据下传速度高,数据量大,持续时间长,并且要求具有差错控制功能。而本文介绍了为了满足此要求而设计的数据接收和存储系统。

系统设计

数据接收和存储系统主要包括数据接收和预处理,数据传送,数据存储等部分。本文主要介绍 CPLD,PCI 总线结构,总线控制器 PCI9054。其系统组成如图 2 所示。

基带串行信号由复杂可编程逻辑器件(CPLD)进行串并转换,变为 8 位数据信号后根据编码方式找到同步帧,并进行预处理,然后传到先入先出存储器 FIFO, 在逻辑控制下将数据送入 PCI 总线控制器 PCI9054,由 9054 采用 DMA 突发方式传输至内存,再存储到 RAID 磁盘阵列。

采用复杂可编程逻辑器件(CPLD)可大大减少复杂的控制,通过 VHDL 语言即可灵活设置控制逻辑。而且随着超大规模集成电路的发展,可编程逻辑器件的发展非常迅速,现已达到数十万门,速度《1ns(管脚之间)。由于高速电路设计中的干扰问题非常严重,因此要尽可能地减少线路设计,所以采用 CPLD 不仅可满足系统要求的复杂的逻辑关系,而且可大大减少布线干扰,调试和更改也非常方便,是今后逻辑控制的发展方向。在本系统中,CPLD 不仅实现串并转换和同步的功能,同时还用以实现数据进入 FIFO 以及由 FIFO 传入 PCI9054 的传输控制逻辑,中断逻辑以及主机对数据传输通道的前端控制。

在总线结构上,由于数据传输速度高,以往的 ISA 总线不能满足要求(ISA 总线最大传输速度 5MB/S),必须采用更快的 PCI 总线结构。PCI 总线协议是 Intel 公司 1992 年提出的,为满足高速数据输入 / 输出要求而设计的一种低成本,高性能的局部总线协议。它是一种独立于处理器的总线结构,具有 32 位或 64 位的复用的数据地址总线,总线上的设备可以以系统总线的速度在相互之间进行数据传输,或直接访问系统内存,可以达到 132MB/s 的数据传输速率(64 位则性能加倍)。采用 PCI 接口的设备必须满足 PCI 接口规范 V2.2 标准。

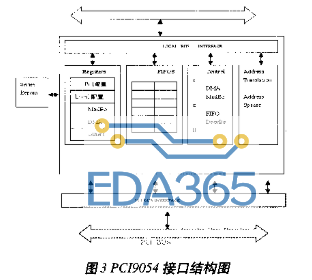

PCI 总线结构具有非常明显的优点,但其总线规范十分复杂,要求非常严格的时序关系,接口的设计难度较大。因此,为了减少 PCI 总线在实际应用中的复杂性,许多公司设计出了专门针对 PCI 总线接口的控制芯片。PCI9054 就是其中比较先进的一种。PCI9054 是 PLX 公司推出的一种 33M, 32 位 PCI 接口控制器,可同时支持 3.3V 和 5V 两种信号环境,并且具有电源管理功能。其结构框图如图 3 所示。

它提供了三种物理总线接口:PCI 总线接口,LOCAL 总线接口,及串行 EPROM 接口。

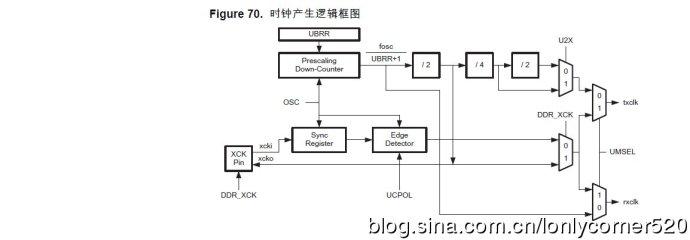

LOCAL 总线的数据宽度为 32 位,时钟频率可达到 50MHZ, 并且支持数据预取功能。 9054 的 LOCAL 总线与 PCI 总线之间数据传输有三种方式:主模式(Direct Master),从模式(Direct Slave),DMA 方式。其内部具有两个 DMA 数据通道,双向数据通路上各有 6 个 FIFO 进行数据缓冲,可同时进行高速的数据接收和发送。8 个 32 位 Maibox 寄存器可为双向数据通路提供消息传送。9054 还有 2 个 32 位 Doorbell 寄存器,用来在 PCI 和 Local 总线上产生中断。

用户通过设置其内部寄存器,即可完成各种控制功能。9054 内部寄存器的配置信息可以写在一片串行 EPROM 中,在加电时 9054 自动加载串行 EPROM 配置信息,并由 PCIBIOS 通过 PCI 总线对配置寄存器读写。9054 可方便地与各种存储设备相连接,在本设计中,它与 FIFO 及 EPROM 的设计接口如图 4 所示。在本系统中,数据传输是单方向的,因此只设计 PCI9504 从 FIFO 中读数据的情况,只用到与读 FIFO 有关的信号,如 REN,RCLK 等。其中的 CPLD 逻辑关系如下:

REN 平时为高电平(无效电平),当 ADS#为低(有效),BLAST 为高(无效),LW/R 为低(有效)时,表明 9054 开始了一个有效的读数据周期,CPLD 产生一个低电平信号 REN(有效电平)给 FIFO,同时作为 Ready 信号返回给 9054,通知 9054 设备已准备就绪。此信号持续到 ADS#为高(无效)且 BLAST 为低(有效)时,表明 9054 已经开始最后一个周期,此时 REN 信号再次变高电平(无效)。

OE 信号与 REN 信号可同样设置,在读信号允许的同时使能 FIFO 芯片。

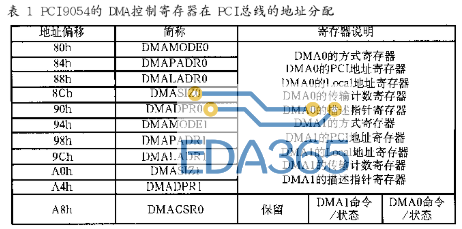

本设计中采用了 PCI9054 的 DMA 工作方式,在此方式下,9054 作为 PCI 总线的主设备,同时也是 Local 总线的控制者,通过设置其 DMA 控制器内部的寄存器即可实现两总线之间的数据传送。表 1 显示了与 DMA 传输相关的寄存器在 PCI 总线上的地址分配:

PCI9054 的 DMA 传输过程可由以下几个步骤实现:

1.设置方式寄存器:设置 DMA 通道的传输方式,寄存器 DMAMODE0 或者 DMAMODE1 的位 9:0- 表示块传输,1- 表示散 / 聚传输;

2.设置 PCI 地址寄存器:设置 PCI 总线侧的地址空间。

3.设置 LOCAL 地址寄存器:设置 LOCAL 总线侧的地址空间。

4.设置传输计数寄存器:以字节位单位设置传输数据量。

5.设置描述寄存器:设置 DMA 传输的方向;在散 / 聚方式下,位 0 表示传输参数的加载地址,0-PCI 地址,1-Local 地址; 位 1 表示传输链结束,0- 未结束,1- 结束;位 2 设置当前块传输结束后中断;位 3 指示 DMA 的传输方向,0- 从 PCI 总线到 Local 总线,1- 从 Local 总线到 PCI 总线;高 28 位[31:4]表示传输参数表的地址指针。

6.设置命令 / 状态寄存器:启动或停止 DMA 操作,并读此寄存器返回 DMA 状态 。

通过 PCI9054 的 DMA 传输方式,高速数据可以较容易地实现从 PCI 接口板上传入计算机,不必考虑 PCI 总线接口的实现,从而大大简化了设计中的复杂度,加快了设计周期。

结语

随着数字技术的发展,要求的数据传输速率将会越来越高,CPLD 技术和 PCI 总线将会越来越多地应用在数据传输的设计中,PCI9054 总线控制器有着较高的性能 / 价格比,将来的应用将会更加广泛。

APP下载

APP下载 登录

登录

热门文章

热门文章