在嵌入式系统中,板上通信接口是指用于将各种集成电路与其他外围设备交互连接的通信通路或总线。

以下内容为常用板上通信接口:包括 I2C、SPI、UART、1-Wire:

I2C 总线

I2C 总线是一种同步、双向、半双工的两线式串行接口总线。这里,半双工的含义是指在任意给定的时刻,只有一个方向上是可以通信的。

I2C 总线最早由 Philips 半导体公司于 20 世纪 80 年代研发面市。I2C 最初的设计目标是为微处理器 / 微控制器系统与电视机外围芯片之间的连接提供简单的方法。

I2C 总线由两条总线组成:串行时钟线 SCL 和串行数据线 SDA。

SCL 线——负责产生同步时钟脉冲。

SDA 线——负责在设备间传输串行数据。

I2C 总线是共享的总线系统,因此可以将多个 I2C 设备连接到该系统上。连接到 I2C 总线上的设备既可以用作主设备,也可以用作从设备。

主设备负责控制通信,通过对数据传输进行初始化 / 终止化,来发送数据并产生所需的同步时钟脉冲。

从设备则是等待来自主设备的命令,并响应命令接收。主设备和从设备都可以作为发送设备或接收设备。无论主设备是作为发送设备还是接收设备,同步时钟信号都只能由主设备产生。

在相同的总线上,I2C 支持多个主设备的同时存在。图 1-1 显示了 I2C 总线上主设备和从设备的连接关系。

当总线空闲时,SDA 和 SCL 都处于高电平状态,当主机要和某个从机通讯时,会先发送一个开始条件,然后发送从机地址和读写控制位,接下来传输数据(主机发送或者接收数据),数据传输结束时主机会发送停止条件。传输的每个字节为 8 位,高位在前,低位在后。

开始条件:SCL 为高电平时,主机将 SDA 拉低,表示数据传输即将开始。

从机地址:主机发送的第一个字节为从机地址,高 7 位为地址,最低位为 R/W 读写控制位,1 表示读操作,0 表示写操作。

一般从机地址有 7 位地址模式和 10 位地址模式两种,如果是 10 位地址模式,第一个字节的头 7 位是 11110XX 的组合,其中最后两位(XX)是 10 位地址的两个最高位,第二个字节为 10 位从机地址的剩下 8 位,如下图所示:

应答信号:每传输完成一个字节的数据,接收方就需要回复一个 ACK(acknowledge)。写数据时由从机发送 ACK,读数据时由主机发送 ACK。当主机读到最后一个字节数据时,可发送 NACK(Notacknowledge)然后跟停止条件。

数据:从机地址发送完后可能会发送一些指令,依从机而定,然后开始传输数据,由主机或者从机发送,每个数据为 8 位,数据的字节数没有限制。

重复开始条件:在一次通信过程中,主机可能需要和不同的从机传输数据或者需要切换读写操作时,主机可以再发送一个开始条件。

停止条件:在 SDA 为低电平时,主机将 SCL 拉高并保持高电平,然后在将 SDA 拉高,表示传输结束。

SPI 总线

SPI 总线是同步、双向、全双工的 4 线式串行接口总线,最早由 Motorola 公司提出。SPI 是由“单个主设备+多个从设备”构成的系统。需要说明的是:在系统中,只要任意时刻只有一个主设备是处于激活状态的,就可以存在多个 SPI 主设备。常运用于 EEPROM、FLASH、实时时钟、AD 转换器、数字信号处理器和数字信号解码器之间实现通信。

为了实现通信,SPI 共有 4 条信号线,分别是:

(1)主设备出、从设备入(Master Out Slave In,MOSI):由主设备向从设备传输数据的信号线,也称为从设备输入(Slave Input/Slave Data In,SI/SDI)。

(2)主设备入、从设备出(Master In Slave Out,MISO):由从设备向主设备传输数据的信号线,也称为从设备输出(Slave Output/Slave Data Out,SO/SDO)。

(3)串行时钟(Serial Clock,SCLK):传输时钟信号的信号线。

(4)从设备选择(Slave Select,SS):用于选择从设备的信号线,低电平有效。

SPI 使用方法:

上图所示芯片有 2 个 SPI 控制器,SPI 控制器对应 SPI 主设备,每个 SPI 控制器可以连接多个 SPI 从设备。挂载在同一个 SPI 控制器上的从设备共享 3 个信号引脚:SCK、MISO、MOSI,但每个从设备的 CS 引脚是独立的 .

主设备通过控制 CS 引脚对从设备进行片选,一般为低电平有效。任何时刻,一个 SPI 主设备上只有一个 CS 引脚处于有效状态,与该有效 CS 引脚连接的从设备此时可以与主设备通信。

所以,SPI 通信方式可以使用“一主多从”的结构进行通信。每个连接到总线上的器件都有唯一的地址,主设备启动数据传输并产生时钟信号,从设备被主设备寻址,同一时刻只允许有一个主设备。

从设备的时钟由主设备通过 SCLK 提供,MOSI、MISO 则基于此脉冲完成数据传输。SPI 的工作时序模式由 CPOL(Clock Polarity,时钟极性)和 CPHA(Clock Phase,时钟相位)之间的相位关系决定,CPOL 表示时钟信号的初始电平的状态,CPOL 为 0 表示时钟信号初始状态为低电平,为 1 表示时钟信号的初始电平是高电平。CPHA 表示在哪个时钟沿采样数据,CPHA 为 0 表示在首个时钟变化沿采样数据,而 CPHA 为 1 则表示在第二个时钟变化沿采样数据。

根据 CPOL 和 CPHA 的不同组合共有 4 种工作时序模式:CPOL=0,CPHA=0、CPOL=0,CPHA=1、CPOL=1,CPHA=0、CPOL=1,CPHA=1

UART

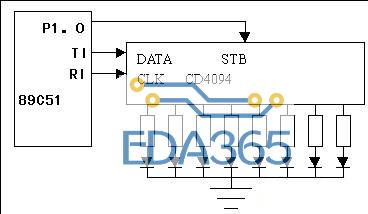

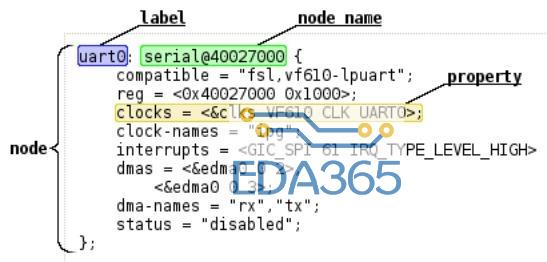

UART——通用异步收发传输器,UART 作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。在应用程序开发过程中使用频率较高的数据总线。

基于 UART 的数据传输是异步形式的串行数据传输。基于 UART 的串行数据传输不需要使用时钟信号来同步传输的发送端和接收端,而是依赖于发送设备和接收设备之间预定义的配置。

对于发送设备和接收设备来说,两者的串行通信配置(波特率、单位字的位数、奇偶校验、起始位数与结束位、流量控制)应该设置为完全相同。通过在数据流中插入特定的比特序列,可以指示通信的开始与结束。当发送一个字节数据的时候,需要在比特流的开头加上起始位,并在比特流的末尾加上结束位。数据字节的最低位紧接在起始位之后。

UART 串口的特点是将数据一位一位地顺序传送,只要 2 根传输线就可以实现双向通信,一根线发送数据的同时用另一根线接收数据。

UART 串口通信有几个重要的参数,分别是波特率、起始位、数据位、停止位和奇偶检验位,对于两个使用 UART 串口通信的端口,这些参数必须匹配,否则通

起始位:表示数据传输的开始,电平逻辑为“0” 。

数据位:可能值有 5、6、7、8、9,表示传输这几个 bit 位数据。一般取值为 8,因为一个 ASCII 字符值为 8 位。

奇偶校验位:用于接收方对接收到的数据进行校验,校验“1” 的位数为偶数(偶校验) 或奇数(奇校验),以此来校验数据传送的正确性,使用时不需要此位也可以。

停止位:表示一帧数据的结束。电平逻辑为“1”。

波特率:串口通信时的速率,它用单位时间内传输的二进制代码的有效位(bit) 数来表示,其单位为每秒比特数 bit/s(bps)。常见的波特率值有 4800、9600、14400、38400、115200 等,数值越大数据传输的越快,波特率为 115200 表示每秒钟传输 115200 位数据。

1-Wire 接口

1-Wire 接口是由 Maxim Dallas 半导体公司(首页为 /zixunimg/eefocusimg/www.maxim-ic.com)开发的异步半双工通信协议,也称为 Dallas 1-Wire®协议。其中,按照主 - 从通信模型,只使用单条信号线 DQ 实现通信。

1-Wire 总线的一个重要特征在于,该总线允许在信号线上传输能量。1-Wire 接口支持在总线上连接单个主设备以及一个或多个从设备。

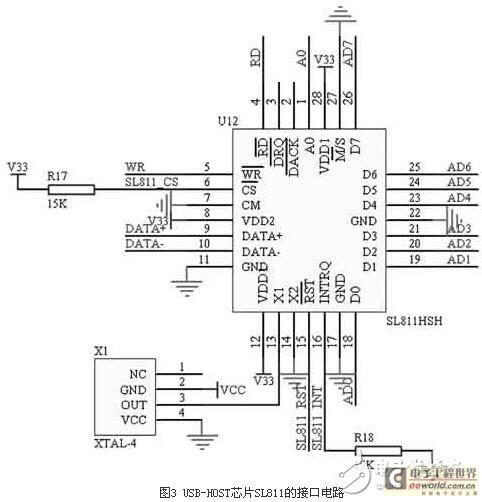

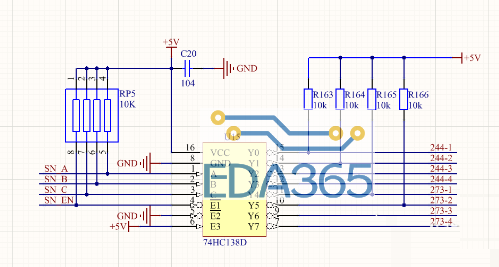

并行接口

板上并行接口(parallel interface)通常用于系统与外围设备之间的通信,其中,外围设备通过存储器映射到系统的主控端。只要嵌入式系统的主控处理器 / 控制器含有并行总线,支持并行总线的设备就可以直接连接到该总线系统上。外围设备与主控端之间具有控制信号接口,可以控制并行总线上的数据通信。这里,通信的控制信号包括读 / 写信号和设备选择信号。一般说来,外围设备具有设备选择线;只有当主控处理器选通该线的时候,该设备才是有效的。

数据传输的方向可以是从主控端到外围设备,也可以是从外围设备到主控端;这是通过读和写控制信号线进行控制的。只有主控处理器能够控制读控制信号和写控制信号。一般说来,外围设备通过存储器映射到主控处理器,从而可以访问分配的地址范围。此时,设备需要使用地址译码电路来产生芯片选择信号。

当处理器选择的地址位于设备指定范围内的时候,译码电路对芯片选择线进行触发,从而激活设备。然后,处理器可以使能相应的控制线(分别是 RD 与 WD),从而由设备读出数据,或者是向设备写入数据。

为了实现并行通信,系统需要严格遵循时序规范。前面已经提到过,并行通信是由主控处理器启动的。如果某外围设备想要对通信进行初始化,那么可以向处理器发出中断,告知相关信息。

为了实现上述功能,设备的中断线需要连接到处理器的中断线上,并且主控处理器需要触发相应的中断。需要说明的是,主控处理器的数据总线宽度决定了并行接口的宽度,可以是 4 位、8 位、16 位、32 位、64 位等。设备支持的总线宽度应该与主控处理器完全相同。

APP下载

APP下载 登录

登录

热门文章

热门文章